# **MCP2140A**

# IrDA<sup>®</sup> Standard Protocol Stack Controller With Fixed 9600 Baud Communication Rate

### **Features**

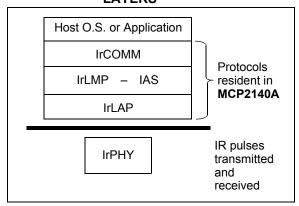

- Implements the IrDA® Protocols, including:

- IrLAP

- IrLMP

- IAS

- Tiny TP

- IrCOMM (9-wire "cooked" service class)

- Provides IrDA standard physical signal layer support including:

- Bidirectional communication

- CRC implementation

- Fixed Data communication rate of 9600 baud

- Includes UART-to-IrDA standard encoder/decoder functionality:

Easily interfaces with industry standard UARTs and infrared transceivers

- Easily communicates with 16-bit PIC Microcontroller IrDA Standard Stack Library

- UART interface for connecting to Data Communications Equipment (DCE) or Data Terminal Equipment (DTE) systems

- Transmit/Receive formats (bit width) supported:

- 1.63 µs (Transmit & Receive)

- 3/16 bit time (Receive Only)

- Hardware UART Support:

- 9.6 kbaud baud rate

- 60 Byte Data Buffer Size (64 Byte Packet)

- · Infrared Supported:

- 9.6 kbaud baud rate

- 64 Byte Packet Size (60 Data Bytes)

- · Operates as Secondary Device

- Wide Operating Voltage: 2.0V to 5.5V

- · Automatic Low Power mode:

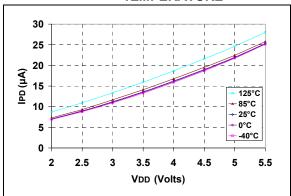

- < 23  $\mu$ A (maximum) @ 2.0V, when no IR activity present (PHACT = L)

- · Footprint Compatibility with MCP2140

# **CMOS Technology**

- Low power, high-speed CMOS technology

- · Low voltage operation

- · Industrial temperature range

- · Low power consumption:

- < 407 µA (maximum) @ 2.0V, 3.6864 MHz

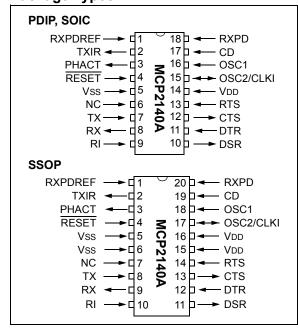

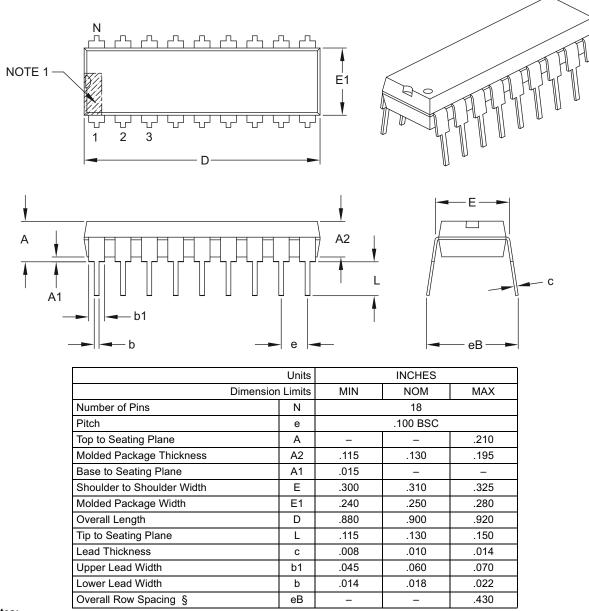

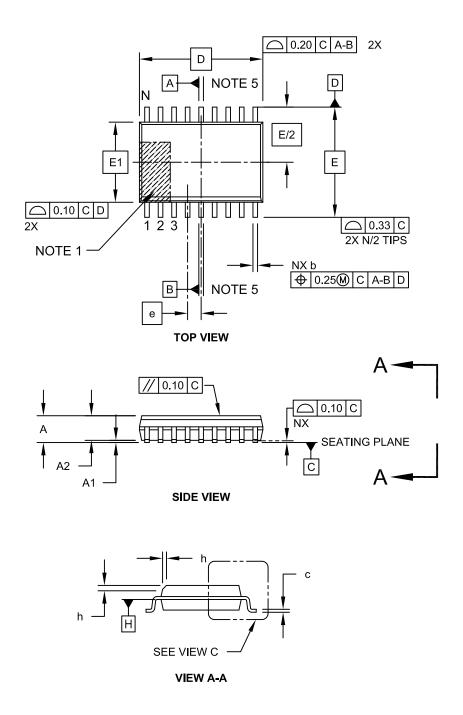

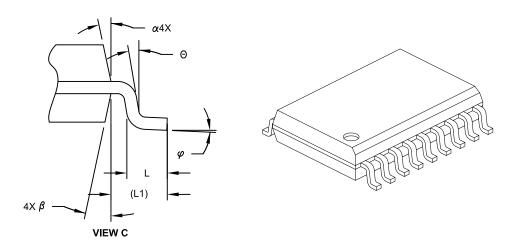

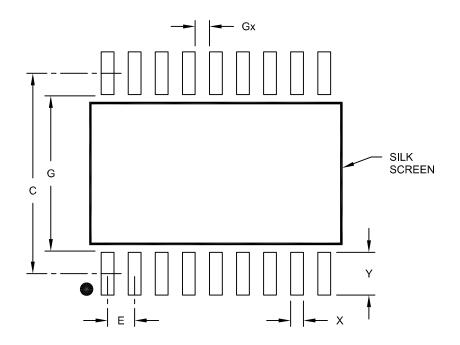

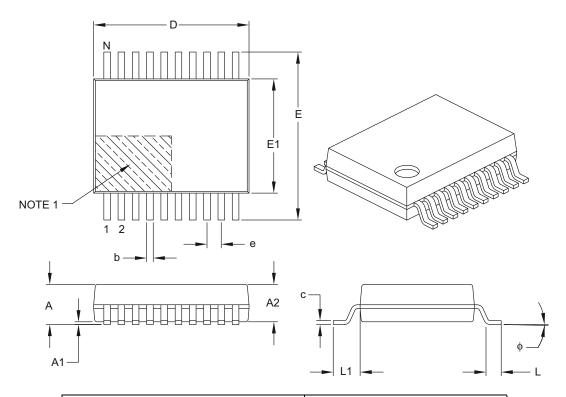

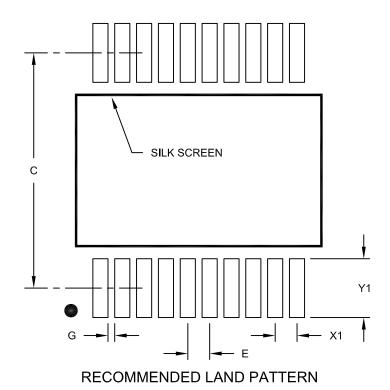

# **Package Types**

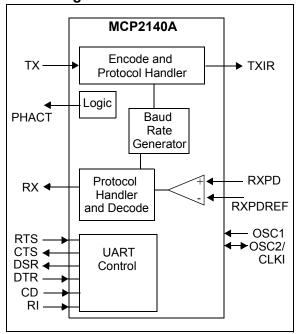

# **Block Diagram**

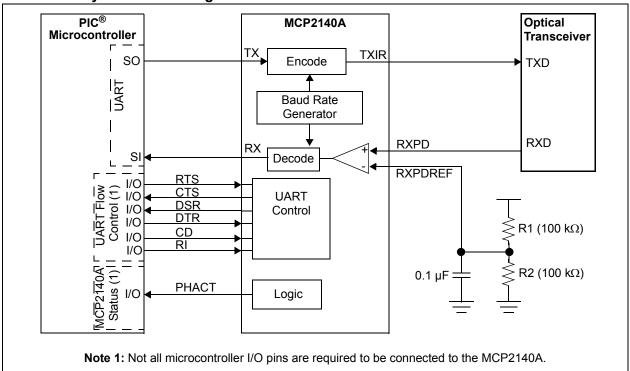

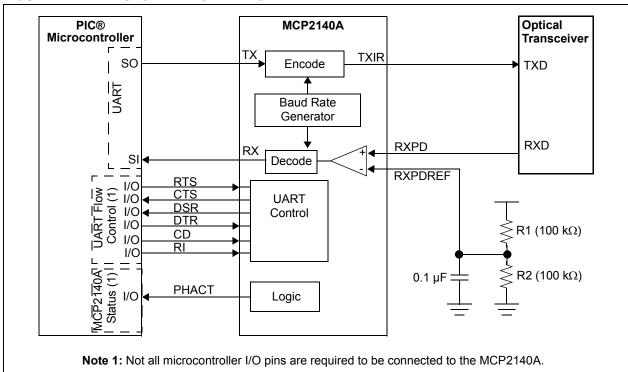

# MCP2140A System Block Diagram

#### 1.0 DEVICE OVERVIEW

The MCP2140A is a cost-effective, low pin count (18-pin), easy-to-use device for implementing IrDA standard wireless connectivity. The MCP2140A provides support for the IrDA standard protocol "stack", bit encoding/decoding and low cost, discrete IR receiver circuitry. The MCP2140A is footprint compatible with the MCP2140. For migration assistance, please refer to Section 2.14 "Migrating from the MCP2140 to the MCP2140A".

The serial and IR interface baud rates are fixed at 9600 baud. The serial interface and IR interface baud rates are dependent on the device frequency, but IrDA standard operation requires a device frequency of 3.6864 MHz.

The MCP2140A will specify the IR baud rate to the primary device during the Discover phase.

The MCP2140A can operate in Data Communication Equipment (DCE) and Data Terminal Equipment (DTE) applications, and resides between a UART and an infrared optical transceiver.

The MCP2140A encodes an asynchronous serial data stream, converting each data bit to the corresponding infrared (IR) formatted pulse. IR pulses received are decoded and then handled by the protocol handler state machine. The protocol handler sends the appropriate data bytes to the host controller in UART formatted serial data.

The MCP2140A supports "point-to-point" applications, that is, one primary device and one secondary device. The MCP2140A operates as a secondary device and does not support "multi-point" applications.

Sending data using IR light requires some hardware and the use of specialized communication protocols. These protocol and hardware requirements are described, in detail, by the IrDA standard specifications. The encoding/decoding functionality of the MCP2140A is designed to be compatible with the physical layer component of the IrDA standard. This part of the standard is often referred to as "IrPHY".

Some of the devices that are compatible with the MCP2140A include:

- · PCs with IR ports

- PDAs

- 16-bit PIC Microcontroller IrDA Standard Stack Library

More information about IrDA standards, specifications and protocols can be found on the IrDA web site at www.IrDA.org.

### 1.1 Applications

The MCP2140A infrared communications controller, supporting the IrDA standard, provides embedded system designers with the easiest way to implement IrDA standard wireless connectivity. Figure 1-1 shows a typical application block diagram, while Table 1-2 shows the pin definitions.

TABLE 1-1: OVERVIEW OF FEATURES

| Features              | MCP2140A                         |

|-----------------------|----------------------------------|

| Serial Communications | UART, IR                         |

| Baud Rate Selection   | Fixed                            |

| Low Power Mode        | Yes - Automatic                  |

| Resets (and Delays)   | RESET, POR<br>(PWRT and OST)     |

| Packages              | 18-pin DIP, SOIC,<br>20-pin SSOP |

Infrared communication is a wireless, two-way data connection using infrared light generated by low-cost transceiver signaling technology. This provides reliable communication between two devices.

Infrared technology offers:

- Universal standard for connecting portable computing devices

- · Easy, effortless implementation

- Economical alternative to other connectivity solutions

- · Reliable, high-speed connections

- Safe to use in any environment (can even be used during air travel)

- No emissions testing needed (FCC, Part 15)

- · Eliminates the hassle of cables

- Allows PCs and other electronic devices (such as PDAs, cell phones, etc.) to communicate with each other

- Enhances mobility by allowing users to easily connect

The MCP2140A allows the easy addition of IrDA standard wireless connectivity to any embedded application that uses serial data. Figure 1-1 shows typical implementation of the MCP2140A in an embedded system.

The IrDA protocol for printer support is not included in the IrCOMM 9-wire "cooked" service class.

FIGURE 1-1: SYSTEM BLOCK DIAGRAM

TABLE 1-2: MCP2140A PIN DESCRIPTION NORMAL OPERATION (DCE)

| Dia Nama | Pin Number |      | Pin Buffer |      |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                     |

|----------|------------|------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | PDIP       | SOIC | SSOP       | Type | Type                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                                                                                         |

| RXPDREF  | 1          | 1    | 1          | I    | А                                                                                                                                                                                                                                                                                                                | IR Receive Photo Detect Diode Reference Voltage. This voltage will typically be in the range of VDD/2.                                                                                                                                                                                              |

| TXIR     | 2          | 2    | 2          | 0    | _                                                                                                                                                                                                                                                                                                                | Asynchronous transmit to IrDA transceiver.                                                                                                                                                                                                                                                          |

| PHACT    | 3          | 3    | 3          | OC   | _                                                                                                                                                                                                                                                                                                                | Protocol Handler Active. Indicates the state of the MCP2140A Protocol Handler. This output is an open collector, so an external pull-up resistor may be required.  1 = Protocol Handler is in the Discovery or NRM state  0 = Protocol Handler is in NDM state or the MCP2140A is in Low Power mode |

| RESET    | 4          | 4    | 4          | I    | ST                                                                                                                                                                                                                                                                                                               | Resets the Device                                                                                                                                                                                                                                                                                   |

| Vss      | 5          | 5    | 5, 6       | _    | Р                                                                                                                                                                                                                                                                                                                | Ground reference for logic and I/O pins                                                                                                                                                                                                                                                             |

| NC       | 6          | 6    | 7          | I    |                                                                                                                                                                                                                                                                                                                  | No connect                                                                                                                                                                                                                                                                                          |

| TX       | 7          | 7    | 8          | I    | TTL                                                                                                                                                                                                                                                                                                              | Asynchronous receive; from host controller UART                                                                                                                                                                                                                                                     |

| RX       | 8          | 8    | 9          | 0    | _                                                                                                                                                                                                                                                                                                                | Asynchronous transmit; to host controller UART                                                                                                                                                                                                                                                      |

| RI       | 9          | 9    | 10         | I    | TTL                                                                                                                                                                                                                                                                                                              | Ring Indicator. The state of this bit is communicated to the IrDA primary device.  1 = No Ring Indicate Present 0 = Ring Indicate Present                                                                                                                                                           |

| DSR      | 10         | 10   | 11         | 0    | Data Set Ready. Indicates that the MCP2140A has established a valid IrDA link with a primary device <sup>(1)</sup> . This signal locally emulated and not related to the DTR bit of the IrDA primary device.  1 = An IR link has not been established (No IR Link) 0 = An IR link has been established (IR Link) |                                                                                                                                                                                                                                                                                                     |

| DTR      | 11         | 11   | 12         | I    | TTL                                                                                                                                                                                                                                                                                                              | Data Terminal Ready. Indicates that the Embedded device connected to the MCP2140A is ready for IR data. The state of this bit is communicated to the IrDA primary device via the IrDA DSR bit carried by IrCOMM.  1 = Embedded device not ready 0 = Embedded device ready                           |

| СТЅ      | 12         | 12   | 13         | 0    | _                                                                                                                                                                                                                                                                                                                | Clear to Send. Indicates that the MCP2140A is ready to receive data from the host controller. This signal is locally emulated and not related to the CTS/RTS bit of the IrDA primary device.  1 = Host controller should not send data 0 = Host controller may send data                            |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

A = Analog

P = Power

CMOS = CMOS compatible input

OC = Open collector output

I = Input

O = Output

**Note 1:** The state of the DSR output pin does not reflect the state of the DTR bit of the IrDA primary device.

# **MCP2140A**

TABLE 1-2: MCP2140A PIN DESCRIPTION NORMAL OPERATION (DCE) (CONTINUED)

| Pin Name    | Pi   | n Numb | er     | Pin  | Buffer                                                                                                                                               |                                                                                                                                                                                                                                                                                        |

|-------------|------|--------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pili Naille | PDIP | SOIC   | SSOP   | Type | Туре                                                                                                                                                 | Description                                                                                                                                                                                                                                                                            |

| RTS         | 13   | 13     | 14     | I    | TTL                                                                                                                                                  | Request to Send. Indicates that a host controller is ready to receive data from the MCP2140A. This signal is locally emulated and not related to the CTS/RTS bit of the IrDA primary device.  1 = Host controller not ready to receive data  0 = Host controller ready to receive data |

| VDD         | 14   | 14     | 15, 16 | _    | Р                                                                                                                                                    | Positive supply for logic and I/O pins.                                                                                                                                                                                                                                                |

| OSC2/CLKI   | 15   | 15     | 17     | I/O  | _                                                                                                                                                    | Oscillator crystal output/external clock source input.                                                                                                                                                                                                                                 |

| OSC1        | 16   | 16     | 18     | I    | CMOS                                                                                                                                                 | Oscillator crystal input.                                                                                                                                                                                                                                                              |

| CD          | 17   | 17     | 19     | -    | ST Carrier Detect. The state of this bit is communicated to the IrDA primary device via the IrDA CD bit.  1 = No carrier present 0 = Carrier present |                                                                                                                                                                                                                                                                                        |

| RXPD        | 18   | 18     | 20     | 1    | A                                                                                                                                                    | IR RX Photo Detect Diode input. This input signal is required to be a pulse to indicate an IR bit. When the amplitude of the signal crosses the amplitude threshold set by the RXPDREF pin, the IR bit is detected.                                                                    |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

A = Analog

P = Power

CMOS = CMOS compatible input

OC = Open collector output

I = Input

O = Output

**Note 1:** The state of the DSR output pin does not reflect the state of the DTR bit of the IrDA primary device.

#### 2.0 DEVICE OPERATION

The MCP2140A serial interface and IR baud rates are fixed at 9600 baud, given a 3.6864 MHz device clock.

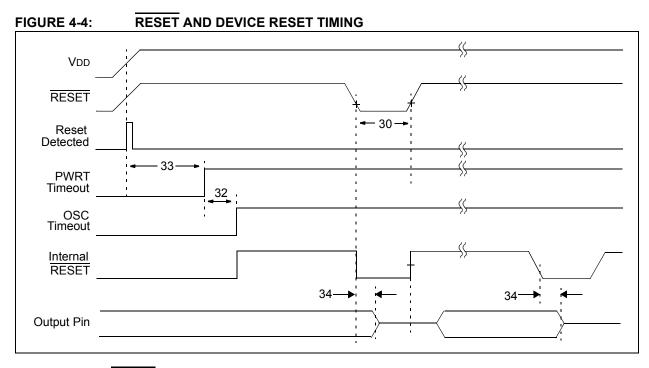

#### 2.1 Power-Up

Any time the device is powered up (Parameter D003), the Power-Up Timer delay (Parameter 33) occurs, followed by an Oscillator Start-up Timer (OST) delay (Parameter 32). Once these delays are complete, communication with the device may be initiated. This communication is from both the infrared transceiver's side and the controller's UART interface.

# 2.1.1 POWER-ON AND BROWN-OUT CONDITIONS

When any state machine is operated outside of its' specified operating conditions, undesired operation may occur. Application validation should be done to determine when the system exits from either a Power-On or a Brown-Out conditions if the MCP2140A requires the use of an external voltage supervisory circuit to ensure proper system operation.

#### 2.2 Device Reset

The MCP2140A is forced into the Reset state when the RESET pin is in the low state. Once the  $\overline{\text{RESET}}$  pin is brought to a high state, the device Reset sequence occurs. Once the sequence completes, functional operation begins.

#### 2.3 Device Clocks

The MCP2140A requires a clock source to operate. This clock source is used to establish the device timing, including the device "Bit Clock".

#### 2.3.1 CLOCK SOURCE

The clock source can be supplied by one of the following:

- Crystal

- Resonator

- · External clock

The frequency of this clock source must be 3.6864 MHz (electrical specification Parameter 1A) for device communication at 9600 baud.

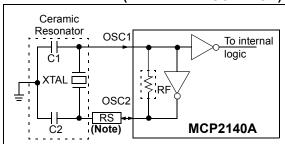

# 2.3.1.1 Crystal Oscillator / Ceramic Resonators

A crystal or ceramic resonator can be connected to the OSC1 and OSC2 pins to establish oscillation (refer to Figure 2-1). The MCP2140A oscillator design requires the use of a parallel-cut crystal. Use of a series cut crystals may give a frequency outside of the crystal manufacturers specifications.

FIGURE 2-1: CRYSTAL OPERATION (CERAMIC RESONATOR)

See Table 2-1 and Table 2-2 for recommended values of C1 and C2

**Note:** A series resistor may be required for AT strip cut crystals.

TABLE 2-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Freq       | OSC1 (C1)  | OSC2 (C2)  |

|------------|------------|------------|

| 3.6864 MHz | 10 - 22 pF | 10 - 22 pF |

Higher capacitance increases the stability of the oscillator, but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

TABLE 2-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Freq       | OSC1 (C1)  | OSC2 (C2)  |

|------------|------------|------------|

| 3.6864 MHz | 15 - 30 pF | 15 - 30 pF |

Note:

Note:

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

# **MCP2140A**

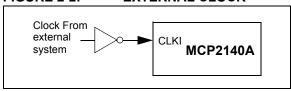

#### 2.3.1.2 External Clock

For applications where a clock is already available elsewhere, users may directly drive the MCP2140A provided that this external clock source meets the AC/DC timing requirements listed in **Section 4.3 "Timing Diagrams and Specifications"**. Figure 2-2 shows how an external clock circuit should be configured.

FIGURE 2-2: EXTERNAL CLOCK

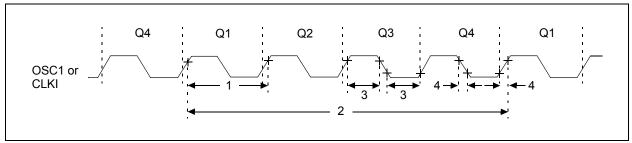

# 2.3.2 BIT CLOCK

The device crystal is used to derive the communication bit clock (BITCLK). There are 16 BITCLKs for each bit time. The BITCLKs are used for the generation of the start bit and the eight data bits. The stop bit uses the BITCLK when the data is transmitted (not for reception).

This clock is a fixed-frequency and has minimal variation in frequency (specified by the crystal manufacturer).

#### 2.4 Host UART Interface

The host UART interface communicates with the host controller. This interface has eight signals associated with it: TX, RX, RTS, CTS, DSR, DTR, CD and RI. Several of these signals are locally generated (not passed over the IR interface). The host UART is a full-duplex interface, meaning that the system can transmit and receive simultaneously.

- **Note 1:** The MCP2140A generates several nondata signals locally.

- 2: The MCP2140A emulates a 3-wire serial connection (TXD, RXD and GND). The transceiver's transmit data (TXD), receive data (RXD) signals, and the state of the CD. RI and DTR input pins are carried back and forth to the primary device.

- **3:** The RTS and CTS signals are local emulations.

#### 2.4.1 BAUD RATE

The baud rate for the MCP2140A serial port (the TX and RX pins) is fixed at 9600 baud when the device frequency is 3.6864 MHz.

#### 2.4.2 TRANSMITTING

When the host controller sends serial data to the MCP2140A, the host controller's baud rate is required to match the baud rate of the MCP2140A's serial port.

### 2.4.3 RECEIVING

When the host controller receives serial data from the MCP2140A, the host controller's baud rate is required to match the baud rate of the MCP2140A's serial port.

# 2.4.4 HARDWARE HANDSHAKING

There are three host UART signals used to control the handshaking operation between the host controller and the MCP2140A.

The following signals are host UART signals:

- DSR

- RTS

- CTS

#### 2.4.4.1 DSR

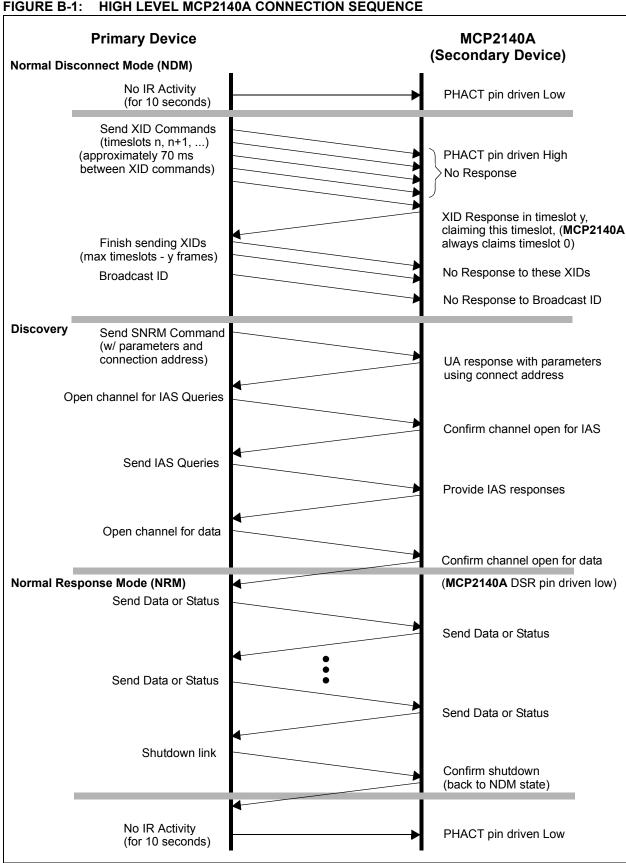

The DSR signal indicates that the MCP2140A has established a link between the MCP2140A and the primary device. Please refer to **Appendix B: "How Devices Connect"** for more information.

#### 2.4.4.2 RTS

The RTS signal indicates to the MCP2140A that the host controller is ready to receive serial data.

Once an IR packet with "data" has been received by the MCP2140A, the RTS signal will need to be low for the received data to be transferred to the host controller. If the RTS signal remains high, an IR link timeout will occur and the MCP2140A will disconnect from the primary device.

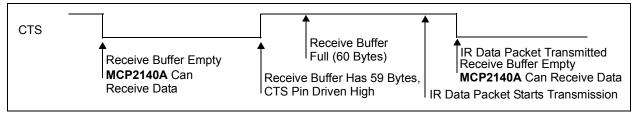

#### 2.4.4.3 CTS

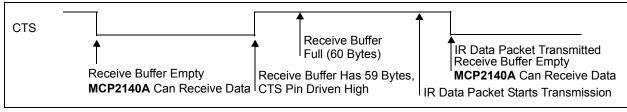

The CTS signal indicates that the MCP2140A UART receive buffer is full. The MCP2140A generates the CTS signal locally.

The MCP2140A UART receive buffer is 60 bytes and the CTS signal will be driven high once 59 bytes have been received.

After the MCP2140A UART has received a byte, there is a latency before the CTS signal is driven high, if the UART receive buffer has 59 bytes. The MCP2140A then supports the reception of another byte (the 60th byte). This allows a byte was being received when CTS was driven high not to be lost. The MCP2140A UART receive buffer supports 60 bytes, regardless if the last byte started transmission before or after the CTS signal was driven high.

**Note:** When the CTS output signal goes high, the UART FIFO will store up to 1 additional byte, for a maximum of 60 bytes.

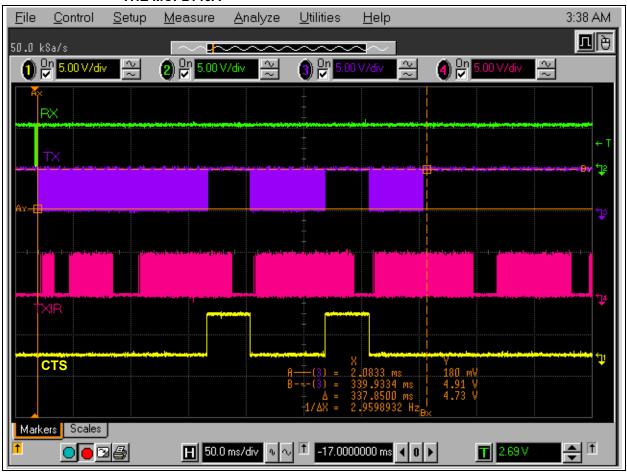

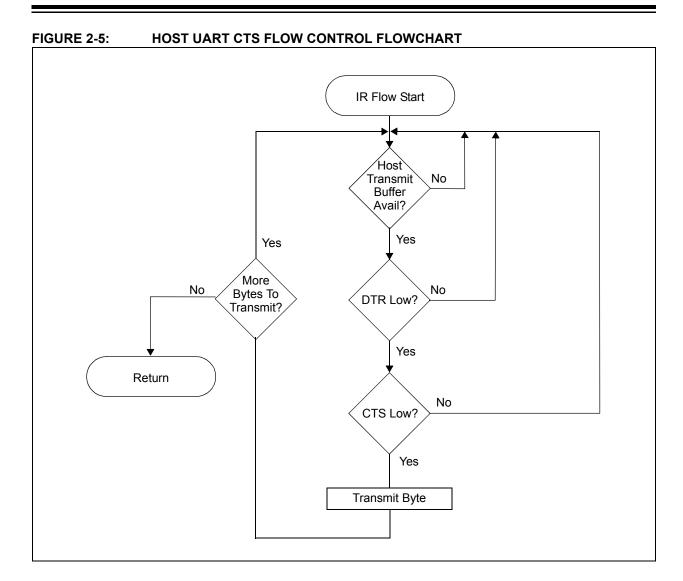

The MCP2140A has a buffer for incoming data from the IR host. This buffer supports the 60-byte data payload plus the memory overhead of the packet. Another 60 byte buffer is provided to buffer data from the UART serial port. The MCP2140A can handle IR data and host UART serial port data simultaneously. A hardware handshaking pin (CTS) is provided to inhibit the host controller from sending serial data when the host UART buffer is not available. Figure 2-3 shows CTS states while Figure 2-4 shows an example of the CTS signal when the host controller streams 250 bytes to the MCP2140A. Figure 2-5 shows a flow chart for host UART flow control using the CTS signal.

FIGURE 2-3: HOST UART CTS SIGNAL AND THE RECEIVE BUFFER

FIGURE 2-4: CTS WAVEFORM FROM HOST CONTROLLER STREAMING OF 250 BYTES TO THE MCP2140A

© 2007-2011 Microchip Technology Inc.

#### 2.5 Encoder/Decoder

The encoder converts the UART format data into the IrDA standard format data and the decoder converts IrDA standard format data into UART format data.

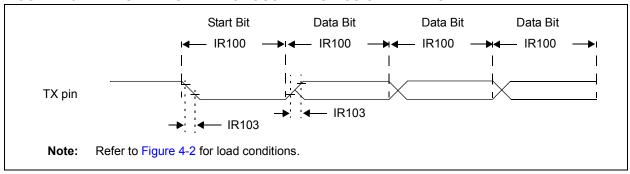

#### 2.5.1 ENCODER (MODULATION)

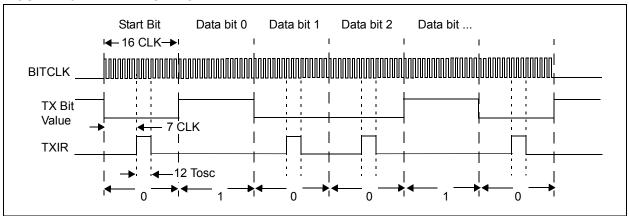

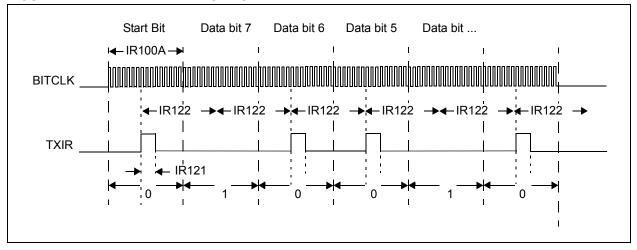

The data that the MCP2140A UART received (on the TX pin) that needs to be transmitted (on the TXIR pin) is modulated. This modulated signal drives the IR transceiver module. Figure 2-6 shows the encoding of the modulated signal.

Note:

The signal on the TXIR pin does not actually line up in time with the bit value that was transmitted on the TX pin, as shown in Figure 2-6. The TX bit value is shown to represent the value to be transmitted on the TXIR pin.

Each bit time is comprised of 16-bit clocks. If the value to be transmitted (as determined by the TX pin) is a logic-low, the TXIR pin will output a low level for 7-bit clock cycles, a logic high level for 3-bit clock cycles or a minimum of 1.6 µs (see Parameter IR121). The remaining 6-bit clock cycles will be low. If the value to transmit is a logic-high, the TXIR pin will output a low level for the entire 16-bit clock cycles.

# FIGURE 2-6: ENCODING

### 2.5.2 DECODER (DEMODULATION)

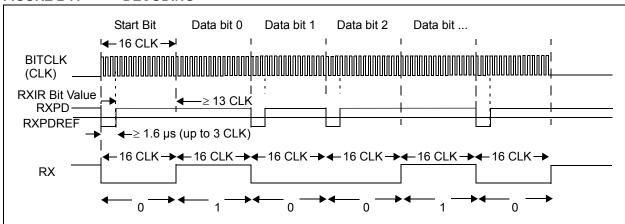

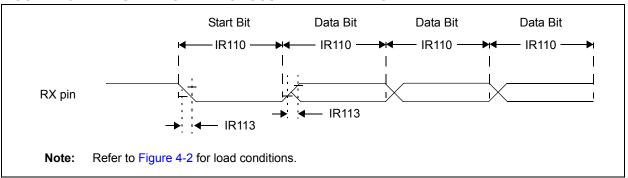

The modulated signal (data) from the IR transceiver module (on the RXIR pin) is demodulated to form the received data (on the RX pin). Once demodulation of the data byte occurs, the data that is received is transmitted by the MCP2140A UART (on the RX pin). Figure 2-7 shows the decoding of the modulated signal.

Note: The signal on the RX pin does not actually line up in time with the bit value that was received on the RXIR pin, as shown in Figure 2-7. The RXIR bit value is shown to represent the value to be transmitted on the RX pin.

Each bit time is comprised of 16-bit clocks. If the value to be received is a logic-low, the RXIR pin will be a low level for the first 3-bit clock cycles, or a minimum of 1.6  $\mu$ s. The remaining 13-bit clock cycles (or difference up to the 16-bit clock time) will be high. If the value to be received is a logic-high, the RXIR pin will be a high level for the entire 16-bit clock cycles. The level on the RX pin will be in the appropriate state for the entire 16 clock cycles.

#### 2.6 IR Port Baud Rate

The baud rate for the MCP2140A IR port (the TXIR and RXIR pins) is fixed at the default rate of 9600 baud. The primary device will be informed of this parameter during NDM. The host UART baud rate and the IR port baud rate are the same.

FIGURE 2-7: DECODING

# 2.7 IrDA Data Protocols Supported by MCP2140A

The MCP2140A supports these required IrDA standard protocols:

- Physical Signaling Layer (PHY)

- Link Access Protocol (IrLAP)

- Link Management Protocol/Information Access Service (IrLMP/IAS)

The MCP2140A also supports some of the optional protocols for IrDA standard data. The optional protocols implemented by the MCP2140A are:

- · Tiny TP

- IrCOMM

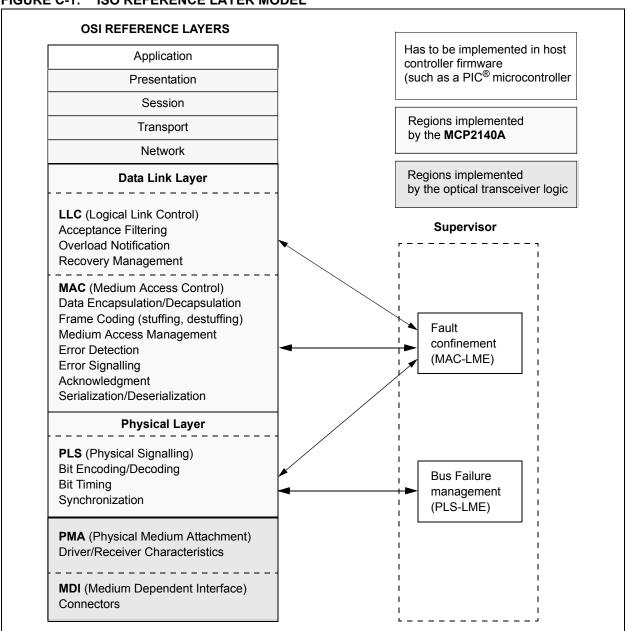

Figure 2-8 shows the IrDA data protocol stack and those components implemented by the MCP2140A.

# FIGURE 2-8: IrDA DATA - PROTOCOL STACKS

| IrTran-P                                                                                    | IrObex                                 | IrLan         | IrCOMM <sup>(1)</sup> |                         | IrMC   |  |

|---------------------------------------------------------------------------------------------|----------------------------------------|---------------|-----------------------|-------------------------|--------|--|

| LM-IAS                                                                                      | Tiny Tr                                | ansport       | Protoc                | ol (Tir                 | ıy TP) |  |

| IRI                                                                                         | Link Mana                              | gement        | - Mux                 | (IrLMF                  | P)     |  |

| IF                                                                                          | R Link Acc                             | ess Pro       | tocol (I              | rLAP)                   |        |  |

| Asynchr<br>Serial IF<br>(9600 -115                                                          | <sup>(2, 3)</sup>                      | Serial IR 4 F |                       | hronous<br>PPM<br>Mb/s) |        |  |

| Supported by the MCP2140A  Optional IrDA data protocols not supported by the MCP2140A       |                                        |               |                       |                         |        |  |

| <b>Note 1:</b> The MCP2140A implements the 9-wire "cooked" service class serial replicator. |                                        |               |                       |                         |        |  |

| 2:                                                                                          | •                                      |               |                       |                         |        |  |

| 3:                                                                                          | 3: An optical transceiver is required. |               |                       |                         |        |  |

#### 2.7.1 IrCOMM

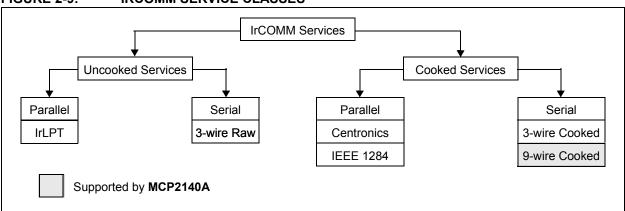

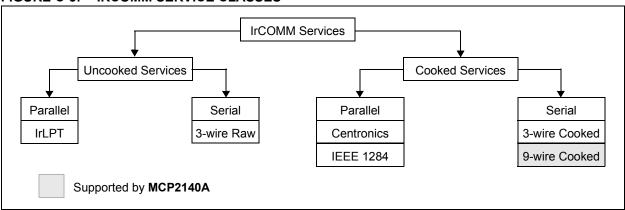

IrCOMM provides the method to support serial and parallel port emulation. This is useful for legacy COM applications, such as printers and modem devices.

The IrCOMM standard is a syntax that allows the primary device to consider the secondary device a serial device. IrCOMM allows for emulation of serial or parallel (printer) connections of various capabilities. The MCP2140A supports the 9-wire "cooked" service class of IrCOMM. Other service classes supported by IrCOMM are shown in Figure 2-9.

The IrDA protocol for printer support is not included in the IrCOMM 9-wire "cooked" service class.

# FIGURE 2-9: IRCOMM SERVICE CLASSES

# 2.8 Minimizing Power

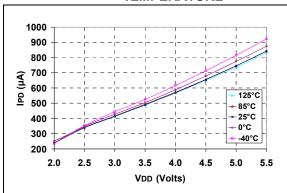

During IR communication between a primary device and the MCP2140A, the MCP2140A is in an operational mode. In this mode, the MCP2140A consumes the operational current (Parameter D010A).

For many applications, the time that IR communication is occurring is a small percentage of the applications operational time. The ability for the IR controller to be in a low power mode during this time will save on the applications power consumption. The MCP2140A will automatically enter a low power mode once IR activity has stopped and will return to operational mode once IR activity is detected on the RXPD and RXPDREF pins. The PHACT pin indicates if the protocol handler is active or inactive (Low Power mode).

Another way to minimize system power is to use an I/O pin of the host controller to enable power to the IR circuity

#### 2.8.1 AUTOMATIC LOW POWER MODE

The Automatic Low Power mode allows the system to achieve the lowest possible operating current.

When the IR link has been "closed", the protocol handler state machine returns to the Normal Disconnect Mode (NDM). During NDM, if no IR activity occurs for about 10 seconds, the device is disabled and enters into Low Power mode. In this mode, the device oscillator is shut down and the PHACT pin will be low (Parameter D010B).

Table 2-3 shows the MCP2140A current. These are specified in Parameter D010A and Parameter D010B.

TABLE 2-3: DEVICE MAXIMUM OPERATING CURRENT

| Mode      | Current | Comment                                                 |

|-----------|---------|---------------------------------------------------------|

| PHACT = H | 407 μΑ  | IR communication is occurring (or waiting for timeout). |

| PHACT = L | 23 μΑ   | No IR communications.                                   |

**Note:** Additional system current is from the receiver/transmitter and the RXPDREF voltage reference circuitry.

# 2.8.2 RETURNING TO DEVICE OPERATION

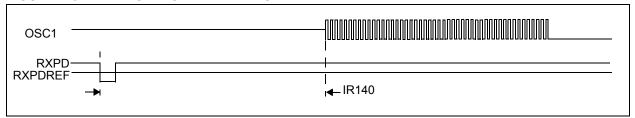

The device will exit the Low Power mode when the RXPD pin voltage crosses the REPDREF pin reference voltage.

A device Reset will also cause the MCP2140A to exit Low Power mode. After device initialization, if no IR activity occurs for about 10 seconds, the device returns to the Low Power mode.

Note: For proper operation, the device oscillator must be within oscillator specification in the time frame specified in Parameter IR140.

#### 2.9 PHACT Signal

The PHACT signal indicates that the MCP2140 protocol handler is active. This output pin is an open collector; so, when interfacing to the host controller, a pull-up resistor is required.

# 2.10 Buffers and Throughput

The IR data rate of the MCP2140A is fixed at 9.6 kbaud. The actual throughput will be less due to several factors. Many significant factors are under the control of the developer. One factor beyond the control of the designer is the overhead associated with the IrDA standard.

Depending on the application, throughput may be an issue in one or both directions.

#### 2.10.1 THROUGHPUT

Throughput is dependant on the direction that the data is streaming and the characteristics of the primary device and secondary device. Streaming throughput from the secondary device may be different with different primary devices. Also streaming throughput from the secondary device may be different than streaming throughput to the secondary device, with the same primary device. Throughput examples are shown in Table 2-4. These examples are based on actual observed data communications.

Note:

IrDA throughput is based on many factors associated with characteristics of the primary and secondary devices. These characteristics may cause your throughput to be more or less than is shown in Table 2-4.

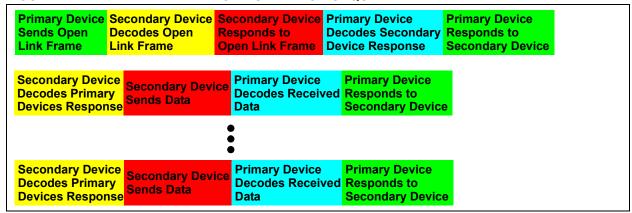

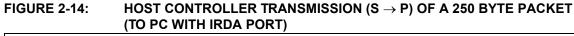

Figure 2-11 shows an example communications sequence between a primary device and a secondary device (MCP2140A). In this example, after the "Primary Device Sends Open Link Frame", the time for the secondary device's response is fixed by the operation of the MCP2140A. After the "Primary Device Decodes Secondary Device Response" the "Primary Device Responds to Secondary Device". Throughput may be improved if the application program can be written so that the primary device response is fast as possible. Also, when the "Secondary Device Sends Data", the frame should have the maximum number of data bytes.

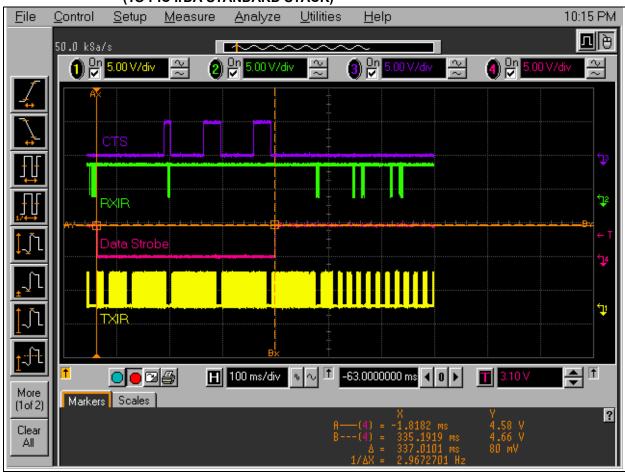

Figure 2-12 shows the screen-capture of a host controller (and MCP2140A) streaming (transmitting) 250 bytes to a primary device (PIC24 + IrDA Standard Stack Library).

Figure 2-13 shows the screen-capture of a MCP2140A (and host controller) receiving 250 streamed bytes from a primary device (PIC24 + IrDA Standard Stack Library).

Figure 2-14 shows a second screen-capture of a host controller (and MCP2140A) streaming (transmitting) 250 bytes to a primary device (PDA HP IPAQ H2495B).

Figure 2-15 shows a second screen capture of a host controller (and MCP2140A) streaming (transmitting) 250 bytes to a primary device (PDA HP IPAQ H2495B).

TABLE 2-4: THROUGHPUT EXAMPLES - 250 BYTES (3)

| Primary Device              | Secondary<br>Device | Data<br>Streaming<br>Direction | 250 Byte<br>Transmit Time<br>(ms) <sup>(1)</sup> | Effective<br>Baud Rate <sup>(2)</sup> | Comment     |

|-----------------------------|---------------------|--------------------------------|--------------------------------------------------|---------------------------------------|-------------|

| PC <sup>(6)</sup>           | MCP2140A (5)        | S -> P                         | 354                                              | 7062                                  | Figure 2-14 |

|                             | MCP2140             | S -> P                         | 650 <sup>(7)</sup>                               | 3692                                  | Note 7      |

| PIC IrDA Standard Stack (4) | MCP2140A (5)        | S -> P                         | 337                                              | 7418                                  | Figure 2-12 |

| PIC IrDA Standard Stack (4) | MCP2140A (5)        | P -> S                         | 549                                              | 4553                                  | Figure 2-13 |

| PDA (HP iPAQ hx2495b)       | MCP2140A (5)        | S -> P                         | 332                                              | 7530                                  | Figure 2-15 |

- Note 1: Measured from Figure. (see comment)

- 2: Interpolated from Figure. (see comment)

- 3: 10 bits transferred for each byte.

- 4: Using the PIC24 Explorer 16 Development Board with IR Transceiver Board

- 5: Using the MCP215X/40 Data Logger Demo Board and Board Firmware V1.4

- 6: IBM 600X Thinkpad (notebook computer) running Windows XP Professional (SP1)

- 7: MCP2140 Data Sheet, DS21790, Table 2-4, MCP2140 transmitted 240 bytes in this transmit time.

### FIGURE 2-10: HOST UART RECEIVE BUFFER AND CTS WAVEFORM

FIGURE 2-11: EXAMPLE IR COMMUNICATION SEQUENCE

FIGURE 2-12: HOST CONTROLLER TRANSMISSION (S  $\rightarrow$  P) OF A 250 BYTE PACKET (TO PIC IrDA STANDARD STACK)

FIGURE 2-13: HOST CONTROLLER RECEPTION (P  $\rightarrow$  S) OF A 250 BYTE PACKET (FROM PIC IRDA STANDARD STACK)

FIGURE 2-15: HOST CONTROLLER TRANSMISSION (S  $\rightarrow$  P) OF A 250 BYTE PACKET (TO PDA HP IPAQ H2495B)

#### 2.10.2 IMPROVING THROUGHPUT

Actual maximum throughput is dependent on several factors, including:

- · Characteristics of the primary device

- Characteristics of the MCP2140A

- · IrDA standard protocol overhead

- · Direction of Data Transmitted

# 2.10.2.1 Characteristics of the Primary Device and the MCP2140A

While the characteristics of the MCP2140A are fixed, the characteristics of the primary device may be made better, or worse, depending on the implementation of the primary device's application program.

IrDA standard protocol overhead limits the maximum throughput to much less then the 9600 baud bit rate.

#### 2.10.2.2 IrDA Standard Protocol Overhead

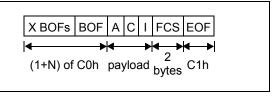

The IrDA standard specifies how the data is passed between the primary device and secondary device. In IrCOMM, an additional 8 bytes are used by the protocol for each packet transfer. In the IrCOMM 9-wire "cooked" service class, 4 bytes of the 64 byte payload are overhead bytes. That leaves a maximum of 60 bytes that can be transferred per "frame".

The most significant factor in data throughput is how well the data frames are filled. If only 1 byte is sent at a time, the throughput overhead of the IrCOMM protocol is 89% (see Table 2-5). The best way to maximize throughput is to align the amounts of data with the receive buffer (IR and host UART) packet size of the MCP2140A.

TABLE 2-5: IRCOMM OVERHEAD %

| MCP2140A             | Data<br>Packet<br>Size<br>(Bytes) | IrCOMM<br>Overhead<br>(Bytes) | IrCOMM<br>Overhead<br>% (1) | Comment           |

|----------------------|-----------------------------------|-------------------------------|-----------------------------|-------------------|

| IR Receive           | 60                                | 8                             | 12 %                        | Note 2            |

|                      | 1                                 | 8                             | 89 %                        |                   |

| Host UART<br>Receive | 60                                | 8                             | 12 %                        | Note 3,<br>Note 4 |

|                      | 1                                 | 8                             | 89 %                        |                   |

Note 1: Overhead % = Overhead /(Overhead + Data).

- **2:** The maximum number of data bytes in the IR receive frame.

- **3:** The maximum number of bytes of the host UART receive buffer.

- **4:** The CTS signal is driven high after the 59 byte.

# 2.10.2.3 Direction of Data Transmitted

Due to the different characteristics of the primary device and the secondary device, the data throughput between two devices may be substantially different depending on the direction the data is being transferred. This is shown in Table 2-4.

#### MCP2140A to Primary Device

One of the factors to improve throughput is to ensure the host controller keeps the MCP2140A UART receive buffer full (60 bytes) to maximize the data bytes sent per IR frame. Figure 2-10 shows the CTS waveform, what the state of the buffers can be and the operation of the host UART and IR interfaces.

The second factor is to minimize the turnaround response time from the primary device, if possible.

#### Primary Device to MCP2140A

In this case, ensure that the host controller can receive data as fast as possible from the MCP2140A without requiring to force the RTS high and delay the data from being received by the host controller.

# 2.10.2.4 From the Primary Device

The MCP2140A uses a fixed IR Receiver data block size of 64 bytes.

The minimum size frame the primary device can respond with is 6 bytes.

#### 2.10.2.5 From the MCP2140A

The MCP2140A uses a fixed host UART receiver data block size of 60 bytes.

#### 2.11 Turnaround Latency

An IR link can be compared to a one-wire data connection. The IR transceiver can transmit or receive, but not both at the same time. A delay of one bit time is recommended between the time a byte is received and another byte is transmitted.

### 2.12 Device ID

The MCP2140A has a fixed Device ID. This Device ID is "MCP2140A XX", with the xx indicating the silicon revision of the device.

### 2.13 Optical Interface

The MCP2140A requires an infrared transceiver for the optical interface. This transceiver can be a single-chip solution (integrated) or be implemented with discrete devices.

The MCP2140A was designed to interface to a integrated optical transceiver, although it can interface to a discrete solution as long as the MCP2140A specifications are meet.

Note: Please refer to Appendix F: "Device Errata" for additional information on the optical transceiver.

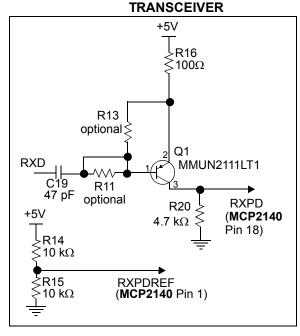

The MCP2140 required a wave shaping circuit to interface to typical integrated optical transceivers. An example circuit is shown in the user guides of the MCP2140 demo and evaluation boards. This circuit is shown in Figure 2-16. This circuit inverts the optical transceivers RXD signal.

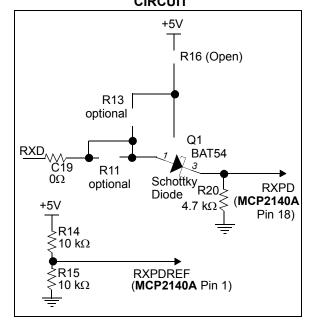

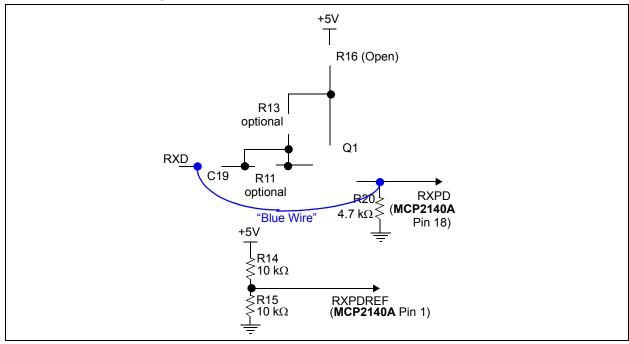

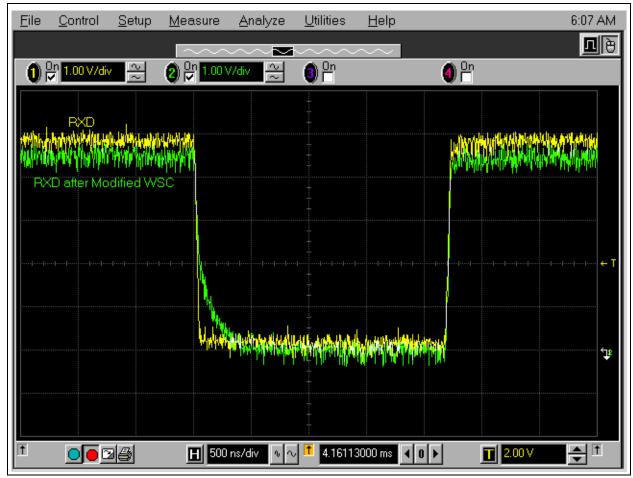

The MCP2140A requires that the RXD signal is not inverted. Figure 2-17 shows how the Microchip example wave shaping circuit can be modified with simple component replacement to support the MCP2140A. Figure 2-19 shows the RXD signal characteristics before and after the modified wave shaping circuit (Figure 2-17).

Table 2-6 shows the schematic symbols for the example MCP2140 wave shaping circuit, and the component changes required to make the PCB layout compatible with the MCP2140A. The layout is not required to be changed since the BAT54 is a Schottky diode in a SOT-23-3 package with the desired pin connections, the capacitor footprint can easily be replaced by a resistor (0 $\Omega$ ), and the R16 resistor can be removed since it is not involved with the circuit.

TABLE 2-6: EXAMPLE MCP2140 WAVE SHAPING CIRCUIT TO MCP2140A COMPONENT CHANGES

|                  | Component                       |                                          |  |  |  |  |

|------------------|---------------------------------|------------------------------------------|--|--|--|--|

| Symbol           | MCP2140 Device (value)          | MCP2140A<br>Device (value)               |  |  |  |  |

| C19              | Capacitor (47pF)                | Resistor $(0 \Omega)^{(1)}$              |  |  |  |  |

| R11              | _                               | _                                        |  |  |  |  |

| R13              | _                               | _                                        |  |  |  |  |

| R16              | Resistor $(100\Omega)$          | _                                        |  |  |  |  |

| R20              | Resistor (4.7 kΩ)               | Resistor<br>(4.7 KΩ) <sup>(1)</sup>      |  |  |  |  |

| Q1<br>(SOT-23-3) | PNP Transistor<br>(MMUN2111LT1) | Schottky Diode<br>(BAT54) <sup>(1)</sup> |  |  |  |  |

**Note 1:** This device is changed from MCP2140 wave shaping circuit implementation.

Figure 2-18 shows a simple "Blue Wire" modification that can be done.

Table 2-8 shows a list of common manufacturers of integrated optical transceivers.

FIGURE 2-16: MCP2140 WAVE SHAPING CIRCUIT FOR INTEGRATED OPTICAL

FIGURE 2-17: MCP2140A

MODIFICATIONS OF

MCP2140 WAVE SHAPING

CIRCUIT

FIGURE 2-18: MCP2140A "BLUE WIRE" MODIFICATIONS OF MCP2140 WAVE SHAPING CIRCUIT

FIGURE 2-19: MCP2140A MODIFICATIONS OF MCP2140 WAVE SHAPING CIRCUIT

# 2.14 Migrating from the MCP2140 to the MCP2140A

This section shows you in the major differences between the MCP2140 and the MCP2140A. Your application may have other sensitivities and a complete system validation should be done.

Table 2-7 shows the differences and enhancements of the MCP2140A in comparison to the MCP2140.

TABLE 2-7: DIFFERENCE BETWEEN MCP2140 AND MCP2140A

|                                              | 10.01 214 | O AILD MICI                      | <b>=</b> 1-107 t       |

|----------------------------------------------|-----------|----------------------------------|------------------------|

| Feature                                      |           | MCP2140                          | MCP2140A               |

| Voltage Rang                                 | е         | 3.0V - 5.5V                      | 2.0V - 5.5V            |

| Frequency of (MHz)                           | Operation | 7.3728                           | 3.6864                 |

| UART operati                                 | ion       | Half Duplex                      | Full Duplex            |

| UART Receiv<br>Size (bytes) (                | 0. 200.   | 29                               | 60 <sup>(2)</sup>      |

| UART Transn<br>Size (bytes) (                |           | 29                               | 60                     |

| IR Receiver F<br>Payload Size<br>(max.)      |           | 64 (3)                           | 64 <sup>(3)</sup>      |

| IR Transmit F<br>Payload Size<br>(max.)      |           | 64 (3)                           | 64 (3)                 |

| Max I <sub>DD</sub> (uA)                     | PHACT = H | 2200                             | 407                    |

| at min. V <sub>DD</sub> .                    | PHACT = L | 60                               | 23                     |

| Integrated Op<br>Transceivers<br>Wave Shapin | RXD       | Required                         | Not<br>Required<br>(1) |

| Optical Trans-<br>bit signal pola            |           | High to Low<br>or<br>Low to High | High to Low<br>only    |

- Note 1: The external wave shaping circuit is not required. For applications replacing the MCP2140, components of the circuit can be replaced to effectively remove the waveshaping circuit. See Section 2.13 "Optical Interface".

- 2: The MCP2140A will drive the CTS signal active after the UART receive buffer has 59 bytes. The Receive buffer supports the reception of a 60th byte for systems that have 0 delay between UART data bytes.

- 3: Includes 4 bytes overhead for 9-wire "cooked" protocol. This means that there are a maximum of 60 data bytes per frame.

# 2.15 The PIC IrDA Standard Stack Library and the MCP2140A

The MCP2140A is compatible with the PIC IrDA Standard Stack Library routines for 16-bit PIC microcontrollers. The application must use the Client Library routines for the IrCOMM 9-wire cooked protocol (for primary device operation).

#### 2.16 References

The IrDA standards organization information can be found at:

### http://www.irda.org

Some common manufacturers of optical transceivers are shown in Table 2-8.

TABLE 2-8: COMMON OPTICAL TRANSCEIVER MANUFACTURERS

| Company               | Company Web Site Address |

|-----------------------|--------------------------|

| Sharp <sup>®</sup>    | www.sharpsma.com         |

| Infineon <sup>®</sup> | www.infineon.com         |

| Agilent <sup>®</sup>  | www.agilent.com          |

| Vishay <sup>®</sup>   | www.vishay.com           |

| Rohm <sup>®</sup>     | www.rohm.com             |

# 3.0 DEVELOPMENT TOOLS

The MCP2140A currently has three Demo/Development boards that can be used to demonstrate or evaluate the MCP2140A. These boards are:

- MCP215x/40 Data Logger Demo Board

- MCP215x/40 Developers Daughter Board

- · MCP2140 Wireless Temp Sensor Demo Board

These boards have not been tested with the MCP2140A. However, the supplied MCP2140 device can easily be replaced with the MCP2140A. The wave-shaping circuit for the MCP2140 will need to be modified. See **Section 2.13 "Optical Interface"** for additional information on modifying the MCP2140 wave shaping circuit.

Please check with the Microchip Technology Inc. web site (www.microchip.com) for additional boards and technical information.

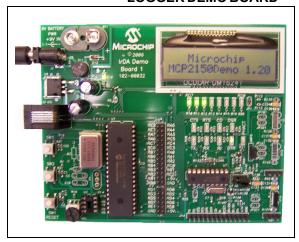

# 3.1 MCP215X/40 Data Logger Demo Board

Part Number: MCP215XDM

**Devices Supported:** MCP2150, MCP2155, MCP2140, and MCP2140A

The MCP215X IrDA Data Logger Demo Board demonstrates the MCP2150 (or MCP2155) IrDA Standard Protocol Stack Controller device in a real world application. The system designer can use this design as an example of how to integrate an IrDA standard port in their embedded system.

Note: Use of the MCP2140A will require that the MCP2140 wave shaping circuit be modified. See Section 2.13.

# FIGURE 3-1: MCP215X/40 DATA LOGGER DEMO BOARD

### Features:

- Demonstrates the MCP2150 IrDA Protocol Controller in a data logging application

- Communicates directly to a Laptop computer, Palm or Pocket PC PDA

- Primary device application programs are provided to demonstrate operation (for PC, Palm OS, Pocket PC)

- F/W routines transmit data to a primary device (i.e., Laptop, PDA)

- · LCD display indicates system state

- Reprogrammable PIC16F877 with ICSP™ (In-Circuit Serial Programming™) interface and ICD header

- Interface Header allows board to be interfaced to a prototype system application

- Header allows other optical transceiver circuits to be interfaced to the MCP215X device

- · Operates on 9V DC input or a 9V battery

# 3.2 MCP215X/40 Developer's Daughter Board

Part Number: MCP215X/40EV-DB

**Devices Supported:** MCP2150, MCP2155, MCP2140, and MCP2140A

The MCP215X/40 Developer's Daughter Board is used to evaluate and demonstrate the MCP2140 IrDA Standard Protocol Stack Controller with encoder/decoder devices.

Headers allow the MCP215X/40 Developer's Daughter Board to be easily jumpered into systems for development purposes.

The MCP215X/40 Developer's Daughter Board is designed to interface to several of the new low-cost Microchip demo boards. These include the PIC18 Explorer Demo Board, the PICDEM™ Full Speed USB Demo Board, the PICDEM 2 Plus Demo Board, and the PICDEM LCD 2 Demo board.

When the MCP215X/40 Developer's Daughter Board is used in conjunction with the PIC18 Explorer Demo Board, the MCP215X or MCP2140 can be connected to either of the UARTs on the PIC18F8772 two or the RX and TX signals can be "crossed" so the MCP215X or MCP2140 device can communicate directly out the PIC18 Explorer Demo Board's UART (DB-9).

FIGURE 3-2: MCP215X/40

DEVELOPER'S

DAUGHTER BOARD

#### Features:

- 18-pin socket for installation of MCP2150, MCP2155, or MCP2140 device

- Three optical transceiver circuits (1 installed)

- MCP2140 optical transceiver waveshaping circuit

- Headers to interface to low-cost PICDEM Demo Boards, including:

- PIC18 Explorer Demo Board

- PICDEM LCD 2 Demo Board

- PICDEM Full Speed USB Demo Board

- PICDEM 2 Plus Demo Board

- Headers to easily connect to the user's embedded system

- Jumpers to select circuit connections between MCP2150, MCP2155, and MCP2140

- Jumpers to select routing of MCP215X/40 signals to the PICDEM demo board headers

- Jumpers to configure the operating mode of the board

# 3.3 MCP2140 IrDA Wireless Temp Sensor Demo Board

Part Number: MCP2140DM-TMPSNS

**Devices Supported: MCP2140 and**

MCP2140A

The MCP2140 IrDA Wireless Temp Sensor Demo Board demonstrates the MCP2140 device in a real world application. The system designer can use this design as an example of how to integrate an IrDA standard port in their system.

**Note:** Use of the MCP2140A will require that the MCP2140 wave shaping circuit be modified. See **Section 2.13**.

FIGURE 3-3: MCP2140 IRDA WIRELESS TEMP SENSOR DEMO

#### Features:

- Demonstrates the MCP2140 IrDA Protocol Controller in a data logging application

- Communicates directly to a laptop computer, Palm or Pocket PC PDA

- Primary device application programs are provided to demonstrate operation (for PC, Palm OS, Pocket PC)

- Demonstrates the MCP2140 IrDA Protocol Controller in a data logging application

- F/W routines transmit TC1047A temperature and other data to a primary device (i.e., laptop, PDA)

- Reprogrammable PIC18F1320 with ICSP™ (In-Circuit Serial Programming™) interface and ICD header

- · Operates on 3 AAA alkaline batteries

# **MCP2140A**

NOTES:

# 4.0 ELECTRICAL CHARACTERISTICS

# **Absolute Maximum Ratings†**

| Ambient Temperature under bias                                                                            | 40°C to +125°C                        |

|-----------------------------------------------------------------------------------------------------------|---------------------------------------|

| Storage Temperature                                                                                       | –65°C to +150°C                       |

| Voltage on VDD with respect to Vss                                                                        | 0.3V to +6.5V                         |

| Voltage on RESET with respect to Vss                                                                      | 0.3V to +14V                          |

| Voltage on all other pins with respect to Vss                                                             | 0.3V to (VDD + 0.3V)                  |

| Total Power Dissipation (1)                                                                               | 800 mW                                |

| Max. Current out of Vss pin                                                                               | 300 mA                                |

| Max. Current into VDD pin                                                                                 | 250 mA                                |

| Input Clamp Current, Iik (VI < 0 or VI > VDD)                                                             | ±20 mA                                |

| Output Clamp Current, Iok (V0 < 0 or V0 > VDD)                                                            | ±20 mA                                |

| Max. Output Current sunk by any Output pin                                                                | 25 mA                                 |

| Max. Output Current sourced by any Output pin                                                             | 25 mA                                 |

| <b>Note 1:</b> Power Dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD | O-VOH) $x$ IOH $\} + \sum(VOL x IOL)$ |

**†NOTICE:** Stresses above those listed under "Maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note: Voltage spikes below  $V_{SS}$  at the RESET pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50 -  $100\Omega$  should be used when applying a "low" level to the RESET pin rather than pulling this pin directly to  $V_{SS}$ .

# 4.1 DC Characteristics

| DC Spec       | cifications |                                              | Electrical Characteristics: Standard Operating Conditions (unless otherwise specified) Operating Temperature: $-40^{\circ}C \le Ta \le +85^{\circ}C$ (industrial) |                    |     |       |                                 |  |

|---------------|-------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|---------------------------------|--|

| Param.<br>No. | Sym         | Characteristic                               | Min                                                                                                                                                               | Typ <sup>(1)</sup> | Max | Units | Conditions                      |  |

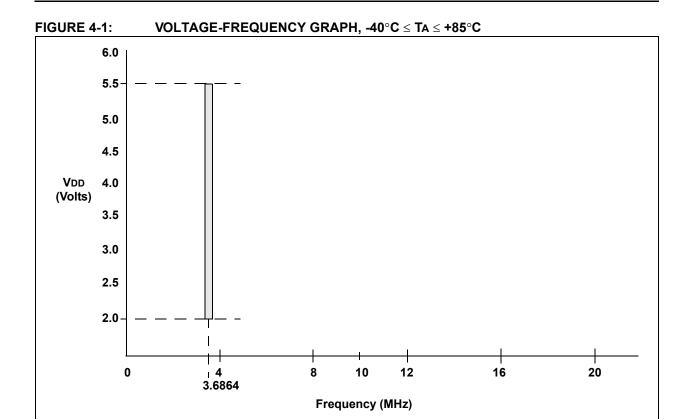

| D001          | VDD         | Supply Voltage                               | 2.0                                                                                                                                                               | _                  | 5.5 | V     | See Figure 4-1                  |  |

| D002          | VDR         | RAM Data Retention<br>Voltage <sup>(2)</sup> | 2.0                                                                                                                                                               | _                  | _   | V     | Device Oscillator/Clock stopped |  |

| D003          | VPOR        | VDD Start Voltage to ensure Power-on Reset   | _                                                                                                                                                                 | Vss                | _   | V     |                                 |  |

| D004          | SVDD        | VDD Rise Rate to ensure Power-on Reset       | 0.05                                                                                                                                                              | _                  | _   | V/ms  |                                 |  |

| D010A         | IDD         | Supply Current (3, 4)                        | _                                                                                                                                                                 | _                  | 23  | μA    | VDD = 2.0V, PHACT = H           |  |

| D010B         |             |                                              | _                                                                                                                                                                 | _                  | 38  | μA    | VDD = 3.0V, PHACT = H           |  |

| D010C         |             |                                              | _                                                                                                                                                                 | _                  | 71  | μA    | VDD = 5.0V, PHACT = H           |  |

| D010D         |             |                                              | _                                                                                                                                                                 | _                  | 350 | μA    | VDD = 2.0V, PHACT = L           |  |

| D010E         |             |                                              | _                                                                                                                                                                 | _                  | 600 | μA    | VDD = 3.0V, PHACT = L           |  |

| D010F         |             |                                              |                                                                                                                                                                   | _                  | 995 | μA    | VDD = 5.0V, PHACT = L           |  |

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered without losing RAM data.

- 3: When the device is in IR communication (PHACT pin is high), supply current is mainly a function of the operating voltage and frequency. Pin loading, pin rate and temperature have an impact on the current consumption. The test conditions for all IDD measurements are made when device is:

OSC1 = external square wave, from rail-to-rail; all input pins pulled to Vss, RXIR = VDD, RESET = VDD;

- **4:** When the device is in low power mode (PHACT pin is low), current is measured with all input pins tied to VDD or Vss and the output pins driving a high or low level into infinite impedance.

# 4.1 DC Characteristics (Continued)

| DC Spec      | cificatio | ns                                      | Electrical Characteristics: Standard Operating Conditions (unless otherwise specified) Operating temperature: $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ (industrial) Operating voltage VDD range as described in DC spec Section 4.1 "DC Characteristics". |     |          |       |                                                      |  |

|--------------|-----------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|------------------------------------------------------|--|

| Param<br>No. | Sym       | Characteristic                          | Min                                                                                                                                                                                                                                                                          | Тур | Max      | Units | Conditions                                           |  |

|              |           | Input Low Voltage                       |                                                                                                                                                                                                                                                                              |     |          |       |                                                      |  |

|              | VIL       | Input pins                              |                                                                                                                                                                                                                                                                              |     |          |       |                                                      |  |

| D030         |           | TX, RI, DTR, RTS, and CD                | Vss                                                                                                                                                                                                                                                                          | _   | 0.8V     | V     | $4.5V \leq V \text{DD} \leq 5.5V$                    |  |

| D030A        |           |                                         | Vss                                                                                                                                                                                                                                                                          | _   | 0.15 VDD | V     | otherwise                                            |  |

| D032         |           | RESET                                   | Vss                                                                                                                                                                                                                                                                          | _   | 0.2 VDD  | V     |                                                      |  |

| D033         |           | OSC1                                    | Vss                                                                                                                                                                                                                                                                          | _   | 0.6      | V     |                                                      |  |

|              |           | Input High Voltage                      |                                                                                                                                                                                                                                                                              |     |          |       |                                                      |  |

|              | VIH       | Input pins                              |                                                                                                                                                                                                                                                                              | _   |          |       |                                                      |  |

| D040         |           | TX, RI, DTR, RTS, and CD                | 0.8 VDD                                                                                                                                                                                                                                                                      | _   | VDD      | V     |                                                      |  |

| D042         |           | RESET                                   | 0.8 VDD                                                                                                                                                                                                                                                                      | _   | Vdd      | V     |                                                      |  |

| D043         |           | OSC1                                    | 1.3                                                                                                                                                                                                                                                                          | _   | Vdd      | V     |                                                      |  |

|              |           | Input Leakage Current (Notes 1, 2)      |                                                                                                                                                                                                                                                                              |     |          |       |                                                      |  |

| D060         | lıL       | TX, RI, DTR, RTS, and CD                | _                                                                                                                                                                                                                                                                            | _   | ±1       | μΑ    | $Vss \leq VPIN \leq VDD, \ pin \ at$ high-impedance. |  |

| D061         |           | RESET                                   | _                                                                                                                                                                                                                                                                            | _   | ±5       | μΑ    | $Vss \le Vpin \le Vdd$                               |  |

| D063         |           | OSC1                                    | _                                                                                                                                                                                                                                                                            | _   | ±5       | μΑ    | $Vss \le Vpin \le Vdd$                               |  |

|              |           | Output Low Voltage                      |                                                                                                                                                                                                                                                                              |     |          |       |                                                      |  |

| D080         | Vol       | TXIR, RX, DSR, and CTS pins             |                                                                                                                                                                                                                                                                              | _   | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V                             |  |

|              |           | Output High Voltage (Note 2)            |                                                                                                                                                                                                                                                                              |     |          |       |                                                      |  |

| D090         | Vон       | TXIR, RX, DSR, and CTS pins             | VDD - 0.7                                                                                                                                                                                                                                                                    |     |          | V     | IOH = -3.0 mA, VDD = 4.5V                            |  |

|              | _         | Capacitive Loading Specs on Output Pins |                                                                                                                                                                                                                                                                              |     |          |       |                                                      |  |

| D101         | Сю        | All Input or Output pins                | _                                                                                                                                                                                                                                                                            | _   | 50       | pF    |                                                      |  |

Note 1: The leakage current on the RESET pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>2:</sup> Negative current is defined as coming out of the pin.

# 4.2 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created following one of the following formats:

# 4.2.1 TIMING CONDITIONS

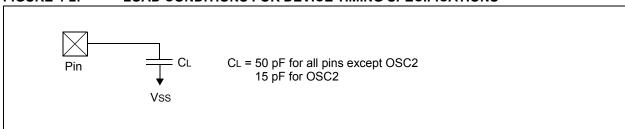

The temperature and voltages specified in Table 4-2 apply to all timing specifications, unless otherwise noted. Figure 4-2 specifies the load conditions for the timing specifications.

TABLE 4-1: SYMBOLOGY

| 1. TppS2p | ppS                                  | 2. TppS |                |

|-----------|--------------------------------------|---------|----------------|

| T         |                                      |         |                |

| F         | Frequency                            | Т       | Time           |

| Е         | Error                                |         |                |

| Lowerca   | ase letters (pp) and their meanings: |         |                |

| рр        |                                      |         |                |

| io        | Input or Output pin                  | osc     | Oscillator     |

| rx        | Receive                              | tx      | Transmit       |

| bitclk    | RX/TX BITCLK                         | RST     | Reset          |

| drt       | Device Reset Timer                   |         |                |

| Upperca   | ase letters and their meanings:      |         |                |

| S         |                                      |         |                |

| F         | Fall                                 | Р       | Period         |

| Н         | High                                 | R       | Rise           |

| I         | Invalid (high-impedance)             | V       | Valid          |

| L         | Low                                  | Z       | High-impedance |

# TABLE 4-2: AC TEMPERATURE AND VOLTAGE SPECIFICATIONS

|                   | Electrical Characteristics:                                         |  |