# Y High Accuracy 8-Channel Parallelable 1A Buck DC/DCs

#### **FEATURES**

- 8-Channel 1A Independent Step-Down DC/DCs

- Master-Slave Configurable for Up to 4A of Output Current with a Single Inductor

- Independent V<sub>IN</sub> Supplies for Each DC/DC (2.25V to 5.5V)

- All DC/DCs Have 0.8V to V<sub>IN</sub> Output Range

- ±1% V<sub>FR</sub> Accuracy, for Buck 1 (1A to 4A)

- ±1% PGOOD Accuracy

- Precision Enable Pin Thresholds for Autonomous Sequencing

- 1MHz to 3MHz Programmable/Synchronizable Oscillator Frequency (2MHz Default)

- Die Temperature Monitor Output

- Thermally Enhanced 38-Lead 5mm × 7mm QFN and TSSOP Packages

- Pin-Compatible with LTC3374

#### **APPLICATIONS**

- General Purpose Multichannel Power Supplies

- Industrial/Automotive/Communications

#### DESCRIPTION

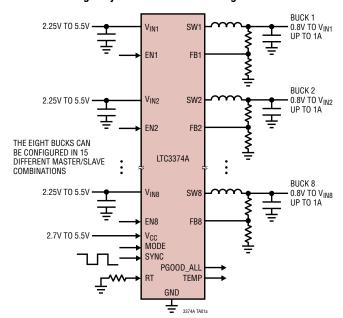

The LTC®3374A is a multioutput power supply IC consisting of eight synchronous 1A buck converters, all powered from independent 2.25V to 5.5V input supplies. An upgraded pin-compatible version of the LTC3374, the LTC3374A, has higher efficiency, improved output voltage accuracy and an added overvoltage (OV) indicator.

The DC/DCs may be used independently or in parallel to achieve higher output currents of up to 4A with a shared inductor. The common buck switching frequency may be programmed with an external resistor, synchronized to an external oscillator, or set to a default internal 2MHz clock. The operating mode for all DC/DCs may be programmed via the MODE pin.

To reduce input noise the buck converters are phased in 90° steps. Precision enable pin thresholds simplify power-up sequencing. The LTC3374A is available in a 38-lead 5mm × 7mm QFN package as well as a 38-lead exposed pad TSSOP package.

T, LT, LTC, LTM, Linear Technology, the Linear logo and Burst Mode are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners

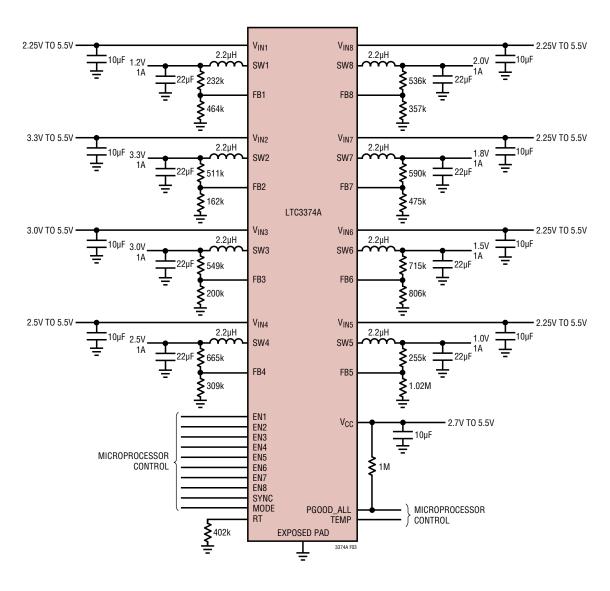

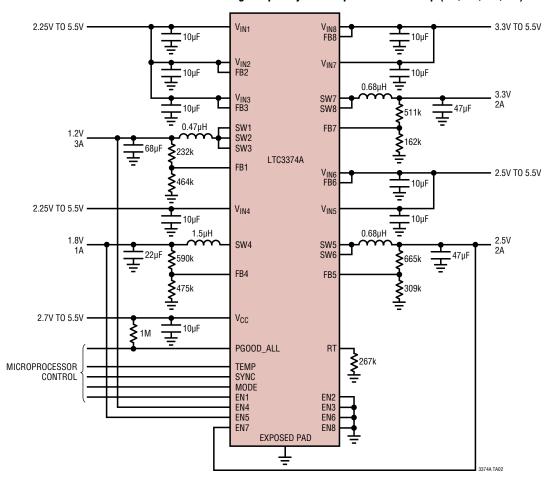

#### TYPICAL APPLICATION

#### **Eight Synchronous 1A Buck Regulators**

3374af

### **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| V <sub>IN1-8</sub> , FB1-8, EN1-8, V <sub>CC</sub> , PGOOD_ALL, | I <sub>SW1-8</sub>                   | 2.6A           |

|-----------------------------------------------------------------|--------------------------------------|----------------|

| SYNC, RT, TEMP0.3V to 6V                                        | Operating Junction Temperature Range |                |

| MODE $-0.3V$ to Lesser of $(V_{CC} + 0.3V)$ or $6V$             | (Notes 2, 3)                         | –40°C to 150°C |

| I <sub>PGOOD_ALL</sub> 5mA                                      | Storage Temperature Range            | –65°C to 150°C |

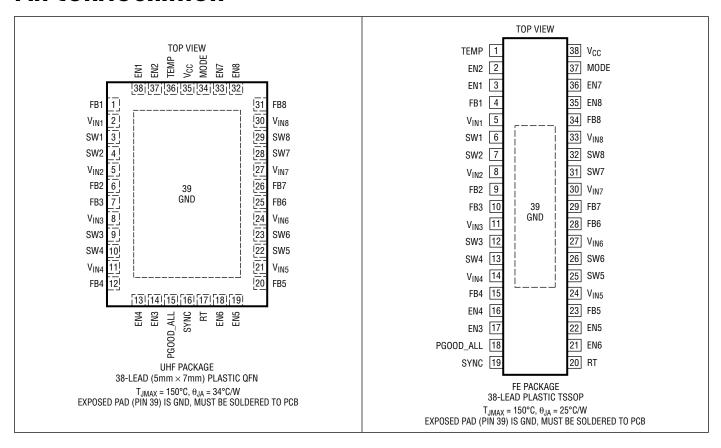

#### PIN CONFIGURATION

### ORDER INFORMATION http://www.linear.com/product/LTC3374A#orderinfo

| LEAD FREE FINISH  | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC3374AEUHF#PBF  | LTC3374AEUHF#TRPBF | 3374A         | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 125°C    |

| LTC3374AIUHF #PBF | LTC3374AIUHF#TRPBF | 3374A         | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 125°C    |

| LTC3374AHUHF #PBF | LTC3374AHUHF#TRPBF | 3374A         | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 150°C    |

| LTC3374AEFE #PBF  | LTC3374AEFE#TRPBF  | LTC3374AFE    | 38-Lead Plastic TSSOP           | -40°C to 125°C    |

| LTC3374AIFE #PBF  | LTC3374AIFE#TRPBF  | LTC3374AFE    | 38-Lead Plastic TSSOP           | -40°C to 125°C    |

| LTC3374AHFE #PBF  | LTC3374AHFE#TRPBF  | LTC3374AFE    | 38-Lead Plastic TSSOP           | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

3374af

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ (Note 2). $V_{CC} = V_{IN1-8} = 3.3V$ , unless otherwise specified.

| SYMBOL             | PARAMETER                                                                                          | CONDITIONS                                                                                                                                            |   | MIN                 | TYP                      | MAX                   | UNITS               |

|--------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------|--------------------------|-----------------------|---------------------|

| $V_{CC}$           | V <sub>CC</sub> Voltage Range                                                                      |                                                                                                                                                       | • | 2.7                 |                          | 5.5                   | V                   |

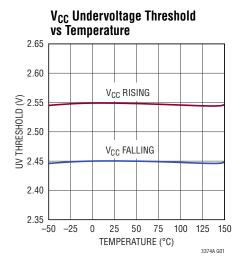

|                    | Undervoltage Lockout (UVLO)<br>Threshold on V <sub>CC</sub>                                        | V <sub>CC</sub> Voltage Falling<br>V <sub>CC</sub> Voltage Rising                                                                                     | • | 2.35<br>2.45        | 2.45<br>2.55             | 2.55<br>2.65          | V                   |

| I <sub>CC</sub>    | V <sub>CC</sub> Input Supply Current                                                               | All Switching Regulators in Shutdown                                                                                                                  |   |                     | 0                        | 1                     | μА                  |

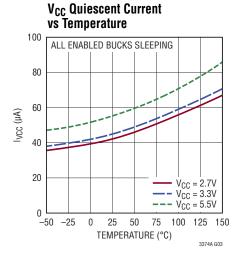

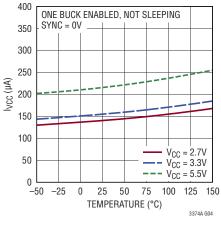

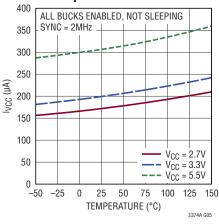

|                    |                                                                                                    | One or More Bucks Active SYNC = 0V, All Enabled Bucks Sleeping One Buck Enabled, Not Sleeping, SYNC = 0V All Bucks Enabled, Not Sleeping, SYNC = 2MHz |   |                     | 45<br>155<br>200         | 75<br>230<br>300      | μΑ<br>μΑ<br>μΑ      |

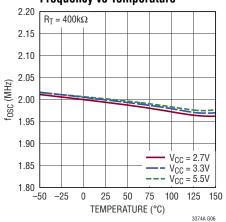

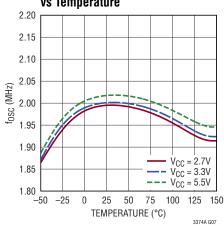

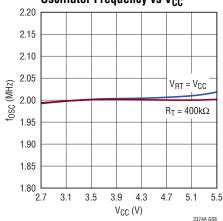

| f <sub>OSC</sub>   | Internal Oscillator Frequency                                                                      | $V_{RT} = V_{CC}$ , SYNC = 0V<br>$V_{RT} = V_{CC}$ , SYNC = 0V<br>$R_T = 400$ k, SYNC = 0V                                                            | • | 1.9<br>1.75<br>1.85 | 2<br>2<br>2              | 2.1<br>2.25<br>2.15   | MHz<br>MHz<br>MHz   |

|                    | Synchronization Frequency                                                                          | $t_{LOW}$ , $t_{HIGH} > 40$ ns                                                                                                                        | • | 1                   |                          | 3                     | MHz                 |

| V <sub>SYNC</sub>  | SYNC Level High<br>SYNC Level Low                                                                  |                                                                                                                                                       | • | 1.2                 |                          | 0.4                   | V                   |

| $V_{RT}$           | RT Servo Voltage                                                                                   | $R_T = 400k$                                                                                                                                          | • | 780                 | 800                      | 820                   | mV                  |

| 1A Buck            | Regulators                                                                                         |                                                                                                                                                       |   |                     |                          |                       |                     |

| V <sub>IN</sub>    | Buck Input Voltage Range                                                                           |                                                                                                                                                       | • | 2.25                |                          | 5.5                   | V                   |

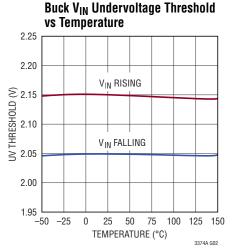

|                    | Undervoltage Lockout (UVLO)<br>Threshold on V <sub>IN</sub>                                        | V <sub>IN</sub> Voltage Falling<br>V <sub>IN</sub> Voltage Rising                                                                                     | • | 1.95<br>2.05        | 2.05<br>2.15             | 2.15<br>2.25          | V                   |

| V <sub>OUT</sub>   | Buck Output Voltage Range                                                                          |                                                                                                                                                       | • | V <sub>FB</sub>     |                          | V <sub>IN</sub>       | V                   |

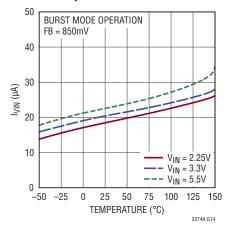

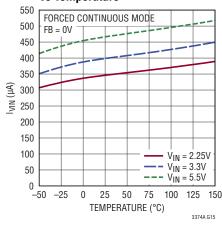

| I <sub>VIN</sub>   | Shutdown Input Current Burst Mode® Operation Burst Mode Operation Forced Continuous Mode Operation | Buck in Regulation, Sleeping Buck in Regulation, Not Sleeping, I <sub>SW</sub> = 0μA (Note 4) I <sub>SW</sub> = 0μA, V <sub>FB</sub> = 0V (Note 4)    |   |                     | 0<br>20.5<br>400<br>400  | 2<br>35<br>550<br>550 | μΑ<br>μΑ<br>μΑ      |

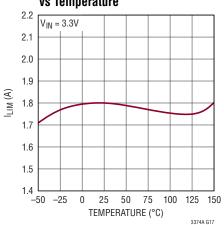

| I <sub>LIM</sub>   | PMOS Current Limit                                                                                 | 1 Buck Converter (Note 5) 2 Buck Converters Combined (Note 5) 3 Buck Converters Combined (Note 5) 4 Buck Converters Combined (Note 5)                 |   | 1.4                 | 1.8<br>3.6<br>5.4<br>7.2 | 2.2                   | A<br>A<br>A         |

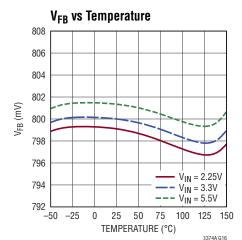

| V <sub>FB1</sub>   | Feedback Regulation Voltage                                                                        | Buck 1<br>Buck 1                                                                                                                                      | • | 796<br>792          | 800<br>800               | 804<br>808            | mV<br>mV            |

| V <sub>FB2-8</sub> | Feedback Regulation Voltage                                                                        | Bucks 2 to 8                                                                                                                                          | • | 784                 | 800                      | 816                   | mV                  |

|                    | Feedback Pin Leakage Current                                                                       |                                                                                                                                                       |   | -50                 | 0                        | 50                    | nA                  |

|                    | Maximum Duty Cycle                                                                                 | $V_{FB} = 0V$                                                                                                                                         | • | 100                 |                          |                       | %                   |

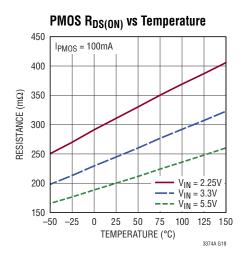

| R <sub>PMOS</sub>  | PMOS On-Resistance                                                                                 | I <sub>SW</sub> = 100mA, V <sub>IN</sub> = 5.0V<br>I <sub>SW</sub> = 100mA, V <sub>IN</sub> = 3.3V                                                    |   |                     | 205<br>245               |                       | $m\Omega$           |

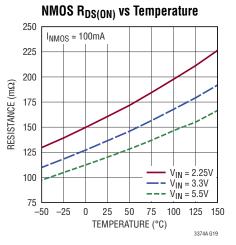

| R <sub>NMOS</sub>  | NMOS On-Resistance                                                                                 | $I_{SW} = 100 \text{mA}, V_{IN} = 5.0 \text{V}$<br>$I_{SW} = 100 \text{mA}, V_{IN} = 3.3 \text{V}$                                                    |   |                     | 125<br>135               |                       | $\Omega$ m $\Omega$ |

|                    | PMOS Leakage Current                                                                               | EN = 0                                                                                                                                                |   | -100                | 0                        | 100                   | nA                  |

|                    | NMOS Leakage Current                                                                               | EN = 0                                                                                                                                                |   | -100                | 0                        | 100                   | nA                  |

|                    | Soft-Start Time                                                                                    | (Note 6)                                                                                                                                              | • | 0.25                | 1.3                      | 3                     | ms                  |

|                    | Rising PGOOD Threshold Voltage                                                                     | Buck 1, as a Percentage of the Regulated $V_{OUT}$ Bucks 2 to 8, as a Percentage of the Regulated $V_{OUT}$                                           | • | 97<br>94            | 98<br>95                 | 99<br>96              | %<br>%              |

|                    | PGOOD Hysteresis                                                                                   | As a Percentage of the Regulated V <sub>OUT</sub>                                                                                                     |   | 0.5                 | 1                        | 1.5                   | %                   |

|                    | Overvoltage Indication                                                                             | As a Percentage of the Regulated V <sub>OUT</sub>                                                                                                     | • | 106                 | 107.5                    | 109                   | %                   |

|                    | Overvoltage Hysteresis                                                                             | As a Percentage of the Regulated V <sub>OUT</sub>                                                                                                     |   | 2                   | 3                        | 4                     | %                   |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{CC} = V_{IN1-8} = 3.3V$ , unless otherwise specified.

| SYMBOL            | PARAMETER                                       | CONDITIONS                                                 |   | MIN        | TYP        | MAX         | UNITS       |

|-------------------|-------------------------------------------------|------------------------------------------------------------|---|------------|------------|-------------|-------------|

| Tempera           | ture Monitor                                    |                                                            |   |            |            |             |             |

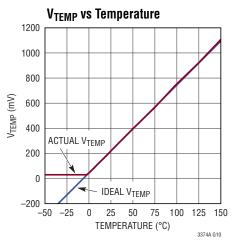

| V <sub>TEMP</sub> | TEMP Voltage at 25°C<br>V <sub>TEMP</sub> Slope |                                                            |   | 200        | 220<br>7   | 240         | mV<br>mV/°C |

| OT                | Overtemperature Shutdown (Note 3)               | Temperature Rising<br>Hysteresis                           |   |            | 170<br>10  |             | 0°<br>0°    |

| Interface         | Logic Pins                                      |                                                            |   |            |            |             |             |

| I <sub>OH</sub>   | Output High Leakage Current                     | 5.5V at the PGOOD_ALL Pin                                  |   | -1         | 0          | 1           | μА          |

| $V_{OL}$          | Output Low Voltage                              | 3mA into the PGOOD_ALL Pin                                 |   |            | 0.1        | 0.4         | V           |

| V <sub>IH</sub>   | Input High Threshold                            | MODE Pin                                                   | • | 1.2        |            |             | V           |

| V <sub>IL</sub>   | Input Low Threshold                             | MODE Pin                                                   | • |            |            | 0.4         | V           |

| I <sub>IH</sub>   | Input High Leakage Current                      | MODE, EN <sub>1-8</sub>                                    |   | -100       | 0          | 100         | nA          |

| I <sub>IL</sub>   | Input Low Leakage Current                       | MODE, EN <sub>1-8</sub>                                    |   | -100       | 0          | 100         | nA          |

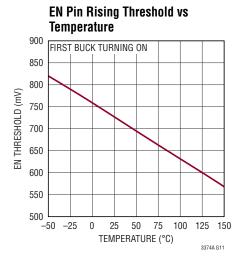

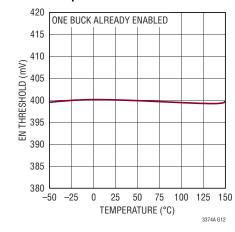

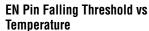

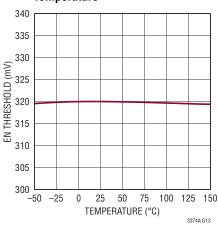

|                   | EN Rising Threshold                             | First Regulator Turning On<br>One Regulator Already in Use | • | 400<br>380 | 730<br>400 | 1200<br>420 | mV<br>mV    |

|                   | EN Falling Threshold                            |                                                            | • | 300        | 320        | 340         | mV          |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3374A is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3374AE is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3374AI is guaranteed over the -40°C to 125°C operating junction temperature range and the LTC3374AH is guaranteed over the -40°C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance, and other environmental factors. The junction temperature ( $T_J$  in °C) is calculated from ambient temperature ( $T_A$  in °C) and power dissipation ( $P_D$  in Watts) according to the formula:

$$T_J = T_A + (P_D \bullet \theta_{JA})$$

where  $\theta_{\text{JA}}$  (in °C/W) is the package thermal impedance.

**Note 3:** The LTC3374A includes overtemperature protection which protects the device during momentary overload conditions. Junction temperatures will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 4:** Static current, switches not switching. Actual current may be higher due to gate charge losses at the switching frequency.

**Note 5:** The current limit features of this part are intended to protect the IC from short term or intermittent fault conditions. Continuous operation above the maximum specified pin current rating may result in device degradation over time.

**Note 6:** The Soft-Start Time is the time from the start of switching until the FB pin reaches 775mV. When a buck is enabled there is a  $100\mu s$  (typical) delay before switching commences.

#### RT Programmed Oscillator Frequency vs Temperature

# Default Oscillator Frequency vs Temperature

#### Oscillator Frequency vs V<sub>CC</sub>

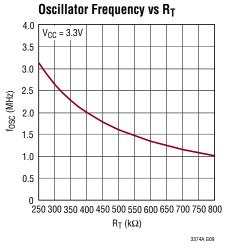

#### EN Pin Rising Threshold vs Temperature

Buck V<sub>IN</sub> Quiescent Current vs Temperature

Buck  $V_{IN}$  Quiescent Current vs Temperature

# PMOS Current Limit vs Temperature

3374af

LINEAR

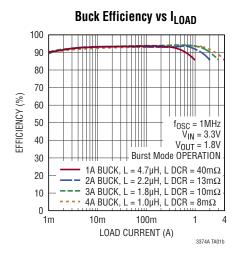

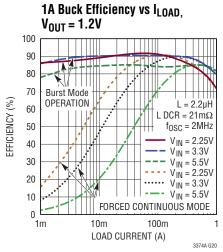

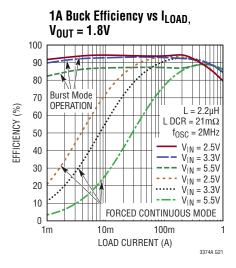

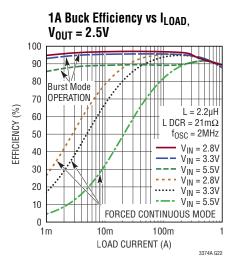

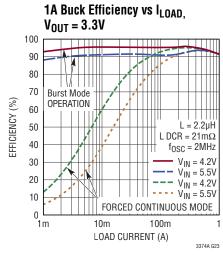

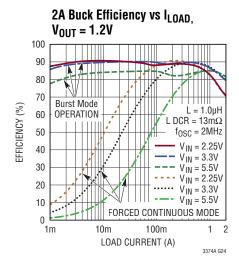

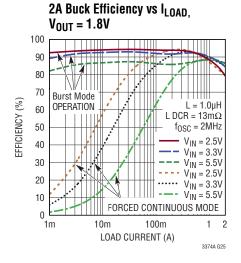

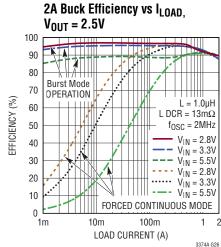

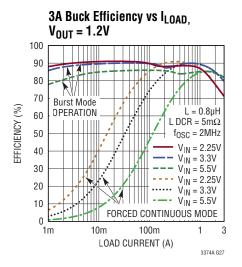

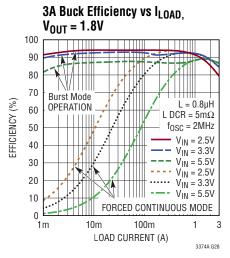

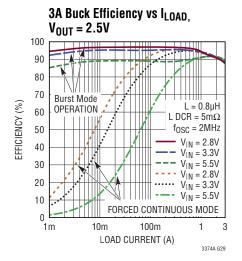

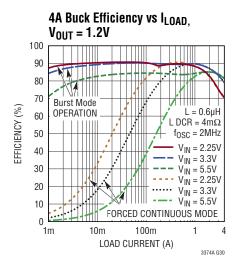

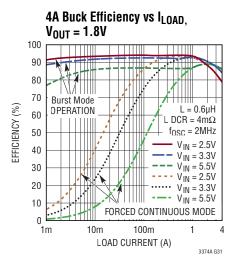

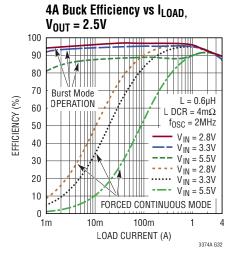

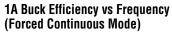

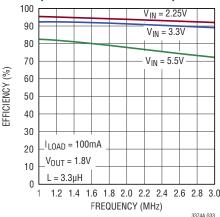

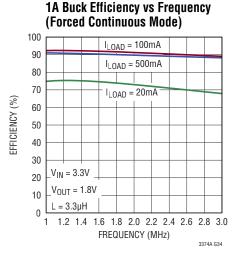

# 1A Buck Efficiency vs I<sub>LOAD</sub> (Across Operating Frequency)

3374af

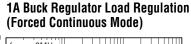

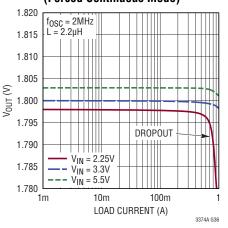

# 4A Buck Regulator Load Regulation (Forced Continuous Mode)

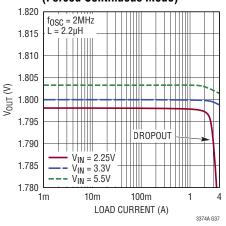

# 1A Buck Regulator Line Regulation (Forced Continuous Mode)

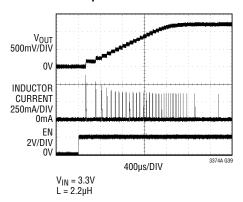

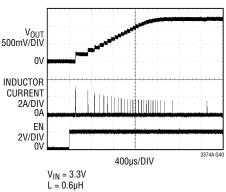

1A Buck Regulator No-Load Start-Up Transient

4A Buck Regulator No-Load Start-Up Transient

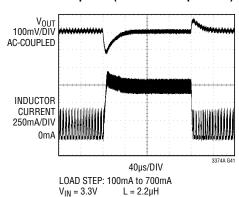

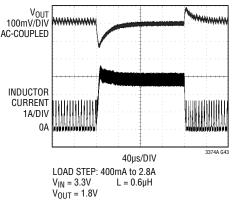

1A Buck Regulator, Transient Response (Burst Mode Operation)

$V_{OUT} = 1.8V$

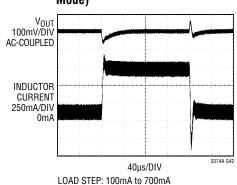

1A Buck Regulator, Transient Response (Forced Continuous Mode)

$L = 2.2 \mu H$

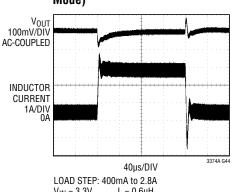

#### 4A Buck Regulator, Transient Response (Burst Mode Operation)

4A Buck Regulator, Transient Response (Forced Continuous Mode)

LOAD STEP: 400mA to 2.8A  $V_{IN}$  = 3.3V L = 0.6 $\mu$ H  $V_{OUT}$  = 1.8V

$V_{IN} = 3.3V$

$V_{OUT} = 1.8V$

#### PIN FUNCTIONS (QFN/TSSOP)

**FB1 (Pin 1/Pin 4):** Feedback Pin for Buck Regulator 1. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground.

$V_{IN1}$  (Pin 2/Pin 5): Buck Regulator 1 Input Supply. Bypass to GND with a 10 $\mu$ F or larger ceramic capacitor.

**SW1 (Pin 3/Pin 6):** Switch Node for Buck Regulator 1. Connect an external inductor to this pin.

**SW2 (Pin 4/Pin 7):** Switch Node for Buck Regulator 2. Connect an external inductor to this pin.

$V_{IN2}$  (Pin 5/Pin 8): Buck Regulator 2 Input Supply. Bypass to GND with a  $10\mu F$  or larger ceramic capacitor. Short to  $V_{IN1}$  when buck regulator 2 is combined with buck regulator 1 for higher current.

**FB2** (Pin 6/Pin 9): Feedback Pin for Buck Regulator 2. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. To combine buck regulator 2 with buck regulator 1 for higher current, connect FB2 to  $V_{IN2}$ . Up to four converters may be combined in this way.

**FB3 (Pin 7/Pin 10):** Feedback Pin for Buck Regulator 3. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. To combine buck regulator 3 with buck regulator 2 for higher current, connect FB3 to  $V_{IN3}$ . Up to four converters may be combined in this way.

$V_{IN3}$  (Pin 8/Pin 11): Buck Regulator 3 Input Supply. Bypass to GND with a 10 $\mu$ F or larger ceramic capacitor. Short to  $V_{IN2}$  when buck regulator 3 is combined with buck regulator 2 for higher current.

**SW3 (Pin 9/Pin 12):** Switch Node for Buck Regulator 3. Connect an external inductor to this pin.

**SW4 (Pin 10/Pin 13):** Switch Node for Buck Regulator 4. Connect an external inductor to this pin.

$V_{IN4}$  (Pin 11/Pin 14): Buck Regulator 4 Input Supply. Bypass to GND with a  $10\mu F$  or larger ceramic capacitor. Short to  $V_{IN3}$  when buck regulator 4 is combined with buck regulator 3 for higher current.

**FB4 (Pin 12/Pin 15):** Feedback Pin for Buck Regulator 4. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. To combine buck regulator 4 with buck regulator 3 for higher current, connect FB4 to  $V_{IN4}$ . Up to four converters may be combined in this way.

**EN4 (Pin 13/Pin 16):** Enable Input for Buck Regulator 4. Active high. Do not float.

**EN3 (Pin 14/Pin 17):** Enable Input for Buck Regulator 3. Active high. Do not float.

**PGOOD\_ALL** (**Pin 15/Pin 18**): PGOOD Status Pin. Opendrain output. When the regulated output voltage of any enabled switching regulator falls below its PGOOD threshold or rises above its overvoltage threshold, this pin is driven LOW. When all buck regulators are disabled PGOOD\_ALL is driven LOW.

**SYNC** (Pin 16/Pin 19): Oscillator Synchronization Pin. Driving SYNC with an external clock signal synchronizes all switchers to the applied frequency. The slope compensation is automatically adapted to the external clock frequency. The absence of an external clock signal enables the frequency programmed by the RT pin. SYNC should be held at ground if not used. Do not float.

RT (Pin 17/Pin 20): Oscillator Frequency Pin. Connect a resistor from RT to ground to program the switching frequency. Tie RT to  $V_{CC}$  to use the default internal 2MHz oscillator. Do not float.

**EN6 (Pin 18/Pin 21):** Enable Input for Buck Regulator 6. Active high. Do not float.

**EN5 (Pin 19/Pin 22):** Enable Input for Buck Regulator 5. Active high. Do not float.

**FB5** (Pin 20/Pin 23): Feedback Pin for Buck Regulator 5. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. To combine buck regulator 5 with buck regulator 4 for higher current, connect FB5 to  $V_{\text{IN5}}$ . Up to four converters may be combined in this way.

LINEAR TECHNOLOGY

#### PIN FUNCTIONS (QFN/TSSOP)

$V_{IN5}$  (Pin 21/Pin 24): Buck Regulator 5 Input Supply. Bypass to GND with a 10 $\mu$ F or larger ceramic capacitor. Short to  $V_{IN4}$  when buck regulator 5 is combined with buck regulator 4 for higher current.

**SW5 (Pin 22/Pin 25):** Switch Node for Buck Regulator 5. Connect an external inductor to this pin.

**SW6 (Pin 23/Pin 26):** Switch Node for Buck Regulator 6. Connect an external inductor to this pin.

$V_{IN6}$  (Pin 24/Pin 27): Buck Regulator 6 Input Supply. Bypass to GND with a 10 $\mu$ F or larger ceramic capacitor. Short to  $V_{IN5}$  when buck regulator 6 is combined with buck regulator 5 for higher current.

**FB6 (Pin 25/Pin 28):** Feedback Pin for Buck Regulator 6. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. To combine buck regulator 6 with buck regulator 5 for higher current, connect FB6 to  $V_{IN6}$ . Up to four converters may be combined in this way.

**FB7 (Pin 26/Pin 29):** Feedback Pin for Buck Regulator 7. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. To combine buck regulator 7 with buck regulator 6 for higher current, connect FB7 to  $V_{IN7}$ . Up to four converters may be combined in this way.

$V_{IN7}$  (Pin 27/Pin 30): Buck Regulator 7 Input Supply. Bypass to GND with a 10 $\mu$ F or larger ceramic capacitor. Short to  $V_{IN6}$  when buck regulator 7 is combined with buck regulator 6 for higher current.

**SW7 (Pin 28/Pin 31):** Switch Node for Buck Regulator 7. Connect an external inductor to this pin.

**SW8 (Pin 29/Pin 32):** Switch Node for Buck Regulator 8. Connect an external inductor to this pin.

$V_{IN8}$  (Pin 30/Pin 33): Buck Regulator 8 Input Supply. Bypass to GND with a 10 $\mu$ F or larger ceramic capacitor. Short to  $V_{IN7}$  when buck regulator 8 is combined with buck regulator 7 for higher current.

**FB8 (Pin 31/Pin 34):** Feedback Pin for Buck Regulator 8. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. To combine buck regulator 8 with buck regulator 7 for higher current, connect FB8 to  $V_{IN8}$ . Up to four converters may be combined in this way.

**EN8 (Pin 32/Pin 35):** Enable Input for Buck Regulator 8. Active high. Do not float.

**EN7 (Pin 33/Pin 36):** Enable Input for Buck Regulator 7. Active high. Do not float.

**MODE** (Pin 34/Pin 37): Mode Selection Logic Input. Programs Burst Mode functionality for all buck switching regulators when the pin is set low. When the pin is set high, all buck switching regulators operate in forced continuous mode.

$V_{CC}$  (Pin 35/Pin 38): Internal Bias Supply. Bypass to GND with a 10 $\mu$ F or larger ceramic capacitor.

**TEMP (Pin 36/Pin 1):** Temperature Indication Pin. TEMP outputs a voltage of 220mV (typical) at 25°C. The TEMP voltage changes by 7mV/°C (typical) giving an external indication of the LTC3374A internal die temperature. Tie TEMP to  $V_{CC}$  to disable the Temperature Monitor and save 12µA (typical) of quiescent current on  $V_{CC}$ .

**EN2 (Pin 37/Pin 2):** Enable Input for Buck Regulator 2. Active high. Do not float.

**EN1 (Pin 38/Pin 3):** Enable Input for Buck Regulator 1. Active high. Do not float.

**GND (Exposed Pad Pin 39/Exposed Pad Pin 39):** Ground. The exposed pad must be connected to a continuous ground plane on the printed circuit board directly under the LTC3374A for electrical contact and rated thermal performance.

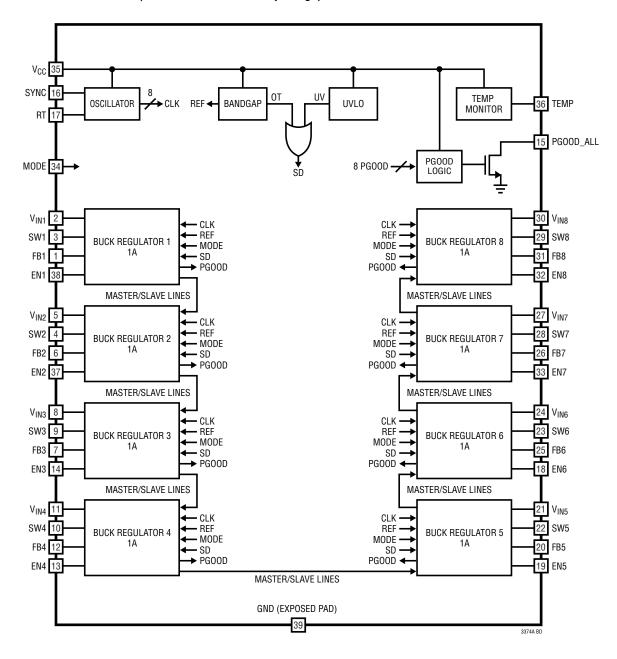

## **BLOCK DIAGRAM** (Pin numbers denote QFN package)

#### **OPERATION**

#### **Buck Switching Regulators**

The LTC3374A is an upgraded, pin-compatible version of the LTC3374 with higher efficiency and improved accuracy. The major differences between them are outlined in Table 1. The LTC3374A contains eight 1A monolithic peak current mode controlled synchronous buck switching regulators. All of the switching regulators are internally compensated and need only external feedback resistors to set the output voltage. The switching regulators offer two operating modes: Burst Mode operation (when the MODE pin is set low) for higher efficiency at light loads and forced continuous PWM mode (when the MODE pin is set high) for lower noise at light loads. The MODE pin collectively sets the operating mode for all enabled buck switching regulators.

In Burst Mode operation at light loads, the output capacitor is charged to a voltage slightly higher than its regulation point. The regulator then goes into a sleep state, during which time the output capacitor provides the load current. In sleep most of the regulator's circuitry is powered down, helping conserve input power. When the output capacitor droops below its programmed value, the circuitry is powered on and another burst cycle begins. The sleep time decreases as load current increases. In Burst Mode operation, the regulator will burst at light loads whereas at higher loads it will operate in constant frequency PWM mode.

In forced continuous mode, the oscillator runs continuously and the buck switch currents are allowed to reverse under light load conditions to maintain regulation. This mode allows the buck to run at a fixed frequency with minimal output ripple.

Table 1. LTC3374A vs LTC3374

| FEATURE                     | LTC3374A | LTC3374 |

|-----------------------------|----------|---------|

| Buck Power Stages           | 8        | 8       |

| Buck 1 Accuracy*            | ±1%      | ±2.5%   |

| Bucks 2-8 Accuracy*         | ±2%      | ±2.5%   |

| PGOOD Buck 1                | 98%      | 92.5%   |

| PGOOD Buck 2                | 95%      | 92.5%   |

| OV Indication               | 107.5%   | -       |

| I <sub>VCC</sub> , Shutdown | 0μΑ      | 8μΑ     |

<sup>\*</sup>Over temperature

Each buck switching regulator has its own V<sub>IN</sub>, SW, FB and EN pins to maximize flexibility. The enable pins have two different enable threshold voltages depending on the operating state of the LTC3374A. With all regulators disabled, the enable pin threshold is set to 730mV (typical). Once any regulator is enabled, the enable pin thresholds of the remaining regulators are set to a bandgap-based 400mV and the EN pins are each monitored by a precision comparator. This precision EN threshold may be used to provide event-based power-up sequencing by connecting the enable pin to the output of another buck through a resistor divider. All buck regulators have forward and reverse-current limiting, soft-start to limit inrush current during start-up, and short-circuit protection. When a buck is enabled there is a 100µs (typical) delay before switching commences and the soft start ramp begins. If a buck is the first one to be enabled there is an additional 1.5ms delay.

The buck switching regulators are phased in 90° steps to reduce noise and input ripple. The phase step determines the fixed edge of the switching sequence, which is when the PMOS turns on. The PMOS off (NMOS on) phase is subject to the duty cycle demanded by the regulator. Bucks 1 and 2 are set to 0°, bucks 3 and 4 are set to 90°, bucks 5 and 6 are set to 180°, and bucks 7 and 8 are set to 270°. In shutdown all SW nodes are high impedance.

#### **OPERATION**

#### **Buck Regulators with Combined Power Stages**

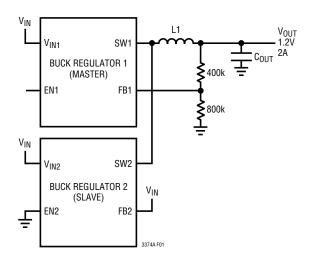

Up to four adjacent buck regulators may be combined in a master-slave configuration by connecting their SW pins together, connecting their  $V_{IN}$  pins together, and connecting the higher numbered bucks' FB pin(s) to the input supply. The lowest numbered buck is always the master. In Figure 1, buck regulator 1 is the master. The feedback network connected to the FB1 pin programs the output voltage to 1.2V. The FB2 pin is tied to  $V_{IN}$ , which configures buck regulator 2 as the slave. The SW1 and SW2 pins must be tied together, as must the  $V_{IN1}$  and  $V_{IN2}$  pins. The slave buck control circuitry draws no DC quiescent current. The enable of the master buck (EN1) controls the operation of the combined bucks; the enable of the slave buck (EN2) must be tied to ground.

Any combination of 2, 3, or 4 adjacent buck regulators may be combined to provide up to 2A, 3A or 4A of output load current, respectively. For example, buck regulator 1 and buck regulator 2 may run independently, while buck regulators 3 and 4 may be combined to provide 2A, while buck regulators 5 through 8 may be combined to provide 4A. Buck regulator 1 is never a slave, and buck regulator 8 is never a master. Fifteen unique output power stage configurations are possible to maximize application flexibility.

Figure 1. Buck Regulators Configured as Master-Slave

#### Power Failure Reporting Via PGOOD ALL Pin

Power failure conditions are reported back via the PGOOD\_ALL pin. All buck switching regulators have an internal power good (PGOOD) signal. When the regulated output voltage of an enabled switcher rises above 98% of its programmed value for Buck 1 or 95% for Bucks 2 through 8, the PGOOD signal transitions high. If the regulated output voltage subsequently falls below 97% of the programmed value for Buck 1 or 94% for Bucks 2 through 8, the PGOOD signal is pulled low. If any internal PGOOD signal stays low for greater than 100µs, then the PGOOD\_ALL pin is pulled low, indicating to a microprocessor that a power failure fault has occurred. The 100µs filter time prevents the pin from being pulled low during a load transient. In addition, whenever PGOOD transitions high there will be a 100µs assertion delay.

The LTC3374A also reports overvoltage conditions at the PGOOD\_ALL pin. If any enabled buck regulator's output voltage rises above 107.5% of the programmed value, the PGOOD\_ALL pin is pulled low after 100µs. Similarly, if all enabled outputs that are overvoltage subsequently fall below 104.5% of the programmed value, the PGOOD\_ALL pin transitions high again after 100µs.

An error condition that pulls the PGOOD\_ALL pin low is not latched. When the error condition goes away, the PGOOD\_ALL pin is released and is pulled high if no other error condition exists. PGOOD\_ALL is also pulled low in the following scenarios: if no buck switching regulators are enabled, if any enabled buck is in UVLO, if the  $V_{CC}$  supply is in UVLO, or if the LTC3374A is in OT (see below).

#### Temperature Monitoring and Overtemperature Protection

To prevent thermal damage to the LTC3374A and its surrounding components, the LTC3374A incorporates an overtemperature (OT) function. When the LTC3374A die temperature reaches 170°C (typical) all enabled buck switching regulators are shut down and remain in shutdown until the die temperature falls to 160°C (typical).

LINEAR TECHNOLOGY

#### **OPERATION**

The die temperature may be read by sampling the analog TEMP pin voltage. The temperature, T, indicated by the TEMP pin voltage is given by:

$$T = \frac{V_{\text{TEMP}} - 45\text{mV}}{7\text{mV}} \bullet 1^{\circ}\text{C}$$

(1)

The typical voltage at the TEMP pin is 220mV at 25°C and is valid for die temperatures higher than 25°C. If temperature monitoring functionality is not needed, then the user may shut down the temperature monitor in order to lower quiescent current (by 12 $\mu$ A typical) by tying TEMP to V<sub>CC</sub>. In this case all enabled buck switching regulators are still shut down when the die temperature reaches 170°C (typical) and remain in shutdown until the die temperature falls to 160°C (typical). If none of the buck switching regulators are enabled, the temperature monitor is shut down to further reduce quiescent current.

#### **Programming the Operating Frequency**

Selection of the operating frequency is a trade-off between efficiency and component size. High frequency operation allows the use of smaller inductor and capacitor values. Operation at lower frequencies improves efficiency by reducing internal gate charge losses but requires larger inductance values and/or capacitance to maintain low output voltage ripple.

The operating frequency for all of the LTC3374A regulators is determined by an external resistor that is connected between the RT pin and ground. The operating frequency is calculated using the following equation:

$$f_{OSC} = 2MHz \left( \frac{400k\Omega}{R_T} \right)$$

(2)

While the LTC3374A is designed to function with operating frequencies between 1 MHz and 3 MHz, it has safety clamps that prevent the oscillator from running faster than 4 MHz (typical) or slower than 250 kHz (typical). Tying the RT pin to  $V_{CC}$  sets the oscillator to the default internal operating frequency of 2 MHz (typical).

The LTC3374A's internal oscillator can alternatively be synchronized through an internal PLL circuit to an external frequency by applying a square wave clock signal to the SYNC pin. During synchronization, the top MOSFET turn-on of buck switching regulators 1 and 2 are locked to the rising edge of the external frequency source. All other buck switching regulators are locked to the appropriate phase of the external frequency source (see Buck Switching Regulators). While syncing, the buck switching regulators operate in forced continuous mode, even if the MODE pin is low. The synchronization frequency range is 1MHz to 3MHz.

After detecting an external clock on the first rising edge of the SYNC pin, the internal PLL starts up at the current frequency being programmed by the RT pin. The internal PLL then requires a certain number of periods to gradually adjust its operating frequency to match the frequency and phase of the SYNC signal.

When the external clock is removed the LTC3374A needs approximately 5µs to detect the absence of the external clock. During this time, the PLL will continue to provide clock cycles before it recognizes the lack of a SYNC input. Once the external clock removal has been identified, the oscillator will gradually adjust its operating frequency to match the desired frequency programmed at the RT pin. SYNC should be connected to ground if not used.

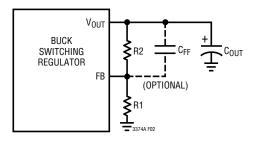

# Buck Switching Regulator Output Voltage and Feedback Network

The output voltage of the buck switching regulators is programmed by a resistor divider connected from the switching regulator's output to its feedback pin and is given by  $V_{OUT} = V_{FB}(1 + R2/R1)$  as shown in Figure 2. Typical values for R1 range from 40k to 1M. The buck regulator transient response may improve with an optional capacitor  $C_{FF}$  that helps cancel the pole created by the feedback resistors and the input capacitance of the FB pin. Experimentation with capacitor values between 2pF and 22pF may improve transient response.

Figure 2. Feedback Components

#### Input and Output Decoupling Capacitor Selection

The LTC3374A has individual input supply pins for each buck switching regulator and a separate  $V_{CC}$  pin that supplies power to all top level control and logic. Each of these pins must be decoupled with low ESR capacitors to GND. These capacitors should be placed as close to the pins as possible. Ceramic dielectric capacitors are a good compromise between high dielectric constant and stability versus temperature and DC bias. Note that the capacitance of a capacitor deteriorates at higher DC bias. It is important to consult manufacturer data sheets to obtain the true capacitance of a capacitor at the operating DC bias voltage. For this reason, avoid the use of Y5V dielectric capacitors. The X5R/X7R dielectric capacitors offer good overall performance.

$V_{CC}$ , pin 35/38, and the input supply voltage pins 2/5, 5/8, 8/11, 11/14, 21/24, 24/27, 27/30, and 30/33 (QFN/TSSOP packages) all need to be decoupled with at least 10 $\mu$ F capacitors. Additionally, all buck regulator outputs should be bypassed with at least 22 $\mu$ F to ground for the 1A configuration.

#### **Combined Buck Regulators**

A single 2A buck regulator can be made by combining two adjacent 1A buck regulators together. Likewise a 3A or 4A buck regulator can be made by combining any three or four adjacent buck regulators, respectively. Tables 3, 4 and 5 show recommended inductors for these configurations.

For a 2A combined buck regulator, the input supply should be decoupled with a  $22\mu F$  capacitor and the output should be decoupled with a  $47\mu F$  capacitor. Similarly, for 3A and 4A configurations, the input and output capacitance should be scaled up to account for the increased load. Refer to the Capacitor Selection section for details on selecting a proper capacitor.

The efficiency of a buck at a given load current may be higher if another buck is combined with it. The combined buck operates at the same load current and that point on its efficiency curve may be higher than that of the single buck. For example, a buck running at a 900mA load may have higher efficiency when two bucks are combined to make a 2A buck, as the 900mA load will be closer to the peak efficiency point of the 2A buck than it was for the 1A buck. It is therefore a good idea to explore combining any unused buck with active bucks in a given application. Otherwise, any unused buck regulator should have it's FB and EN pins tied to ground. The  $V_{\rm IN}$  pin may be tied to ground and the SW pin can float.

#### **Buck Regulators**

All eight buck regulators are optimized to be used with a 2.2 $\mu$ H inductor in the 1A, 2MHz configuration. For operation at different frequencies, the inductor value should be scaled inversely proportional to the switching frequency. For combined buck regulators, the inductor value should also be scaled inversely proportional to the number of combined stages. For example, both a 1A buck running at 2MHz and a 2A buck running at 1MHz should use a 2.2 $\mu$ H inductor. Choose the nearest standard value inductor for the desired configuration. Scaling the inductor for different configurations maintains good transient response. Tables 2, 3, 4 and 5 show recommended inductor values for the different configurations.

LINEAR TECHNOLOGY

3374a1

Table 2. Recommended Inductors for 1A Buck Regulators

| fosc    | PART NUMBER         | L (µH) | MAX I <sub>DC</sub> (A) | MAX DCR (mΩ) | SIZE IN mm (L $\times$ W $\times$ H) | MANUFACTURER     |

|---------|---------------------|--------|-------------------------|--------------|--------------------------------------|------------------|

| 1MHz    | XFL4020-472ME       | 4.7    | 2.7                     | 57.4         | 4 × 4 × 2.1                          | CoilCraft        |

| TIVITIZ | 74408943047         | 4.7    | 2.2                     | 52           | $4.8 \times 4.8 \times 3.8$          | Wurth Elektronik |

|         | XFL4020-222ME       | 2.2    | 3.7                     | 23.5         | 4 × 4 × 2.1                          | CoilCraft        |

| 2MHz    | DFE252012P-2R2M     | 2.2    | 2.2                     | 84           | 2.5 × 2.0 × 1.2                      | Toko             |

|         | IHLP1212BZER2R2M-11 | 2.2    | 3                       | 46           | 3 × 3.65 × 2.0                       | Vishay           |

| 3MHz    | 74438336015         | 1.5    | 3.7                     | 39           | 3 × 3 × 2                            | Wurth Elektronik |

| SIVITIZ | DFE252012F-1R5M     | 1.5    | 2.7                     | 58           | 2.5 × 2 ×1.2                         | Toko             |

#### Table 3. Recommended Inductors for 2A Buck Regulators

| fosc    | PART NUMBER         | L (µH) | MAX I <sub>DC</sub> (A) | MAX DCR (mΩ) | SIZE IN mm (L $\times$ W $\times$ H) | MANUFACTURER     |

|---------|---------------------|--------|-------------------------|--------------|--------------------------------------|------------------|

| 1MHz    | XEL4020-222ME       | 2.2    | 5.5                     | 38.7         | 4 × 4 × 2.1                          | CoilCraft        |

| TIVITIZ | 74438356022         | 2.2    | 4.7                     | 35           | 4.1 × 4.1 × 2.1                      | Wurth Elektronik |

|         | XFL4020-102ME       | 1      | 5.4                     | 11.9         | 4 × 4 × 2.1                          | CoilCraft        |

| 2MHz    | IHLP1212BZER1R0M-11 | 1      | 4.5                     | 24           | 3 × 3.65 × 2.0                       | Vishay           |

|         | SPM4020T-1R0M-LR    | 1      | 5.6                     | 28.1         | 4.1 × 4.4 × 2                        | TDK              |

| 3MHz    | 744383360068        | 0.68   | 4.5                     | 27           | 3 × 3 × 2                            | Wurth Elektronik |

| SIVITZ  | IHLP1212AEERR68M-11 | 0.68   | 5.4                     | 22           | 3 × 3.65 × 1.5                       | Vishay           |

#### Table 4. Recommended Inductors for 3A Buck Regulators

| fosc    | PART NUMBER         | L (µH) | MAX I <sub>DC</sub> (A) | MAX DCR (mΩ) | SIZE IN mm (L $\times$ W $\times$ H) | MANUFACTURER     |

|---------|---------------------|--------|-------------------------|--------------|--------------------------------------|------------------|

| 48411-  | XEL4020-152ME       | 1.5    | 7.4                     | 23.6         | 4 × 4 × 2.1                          | CoilCraft        |

| 1MHz    | IHLP2020CZER1R5M11  | 1.5    | 7                       | 18.5         | 5.18 × 5.49 × 3                      | Vishay           |

|         | XEL4020-821ME       | 0.82   | 10.2                    | 13           | 4 × 4 × 2                            | CoilCraft        |

| 2MHz    | FDV0530-H-R75M      | 0.75   | 9.7                     | 7.6          | 6.2 × 5.8 × 3                        | Toko             |

|         | 744383560068        | 0.68   | 8.2                     | 9            | 4.1 × 4.1 × 2.1                      | Wurth Elektronik |

| 3MHz    | FDSD0420D-R47M      | 0.47   | 6.8                     | 18           | 4.2 × 4.2 × 2                        | Toko             |

| SIVITIZ | IHLP1212AEERR47M-11 | 0.47   | 6.7                     | 15           | 3 × 3.65 × 1.5                       | Vishay           |

#### Table 5. Recommended Inductors for 4A Buck Regulators

| fosc          | PART NUMBER      | L (µH) | MAX I <sub>DC</sub> (A) | MAX DCR (mΩ) | SIZE IN mm (L $\times$ W $\times$ H) | MANUFACTURER     |

|---------------|------------------|--------|-------------------------|--------------|--------------------------------------|------------------|

| 1 1 1 1 1 1 → | XEL4020-102ME    | 1      | 9                       | 14.6         | 4 × 4 × 2.1                          | CoilCraft        |

| 1MHz          | 744316100        | 1      | 11.5                    | 5.225        | 5.3 × 5.5 × 4.0                      | Wurth Elektronik |

|               | XEL4020-561ME    | 0.56   | 11.3                    | 8.8          | 4 × 4 × 2.1                          | CoilCraft        |

| 2MHz          | FDV0530-H-R56M   | 0.56   | 11.1                    | 6.3          | 6.2 × 5.8 × 3                        | Toko             |

|               | SPM4020T-R47M-LR | 0.47   | 8.7                     | 11.8         | 4.1 × 4.4 × 2                        | TDK              |

| 01/11-        | XEL4014-331ME    | 0.33   | 9                       | 12           | 4 × 4 × 1.4                          | CoilCraft        |

| 3MHz          | 744383560033     | 0.33   | 9.6                     | 7.2          | 4.1 × 4.1 × 2.1                      | Wurth Elektronik |

#### **PCB Considerations**

When laying out the printed circuit board, the following list should be followed to ensure proper operation of the LTC3374A:

- 1. The exposed pad of the package (Pin 39) should connect directly to a large ground plane to minimize thermal and electrical impedance. See the Linear Technology Application Note, *Application Notes for Thermally Enhanced Leaded Plastic Packages*, for the proper size and layout of the thermal vias and solder stencils.

- 2. All the input supply pins should each have a local decoupling capacitor.

- 3. The connections to the switching regulator input supply pins and their respective decoupling capacitors should be kept as short as possible. The GND side of these capacitors should connect directly to the ground plane of the part. These capacitors provide the AC current to the internal power MOSFETs and their drivers. It is

- important to minimize inductance from these capacitors to the  $V_{\text{IN}}$  pins of the LTC3374A.

- 4. The switching power traces connecting SW1, SW2, SW3, SW4, SW5, SW6, SW7, and SW8 to their respective inductors should be minimized to reduce radiated EMI and parasitic coupling. Due to the large voltage swing of the switching nodes, high input impedance sensitive nodes, such as the feedback nodes, should be kept far away or shielded from the switching nodes or poor performance could result.

- 5. The GND side of the switching regulator output capacitors should connect directly to the thermal ground plane of the part. Minimize the trace length from the output capacitor to the inductor(s)/pin(s).

- 6. In a combined buck regulator application the trace length of switch nodes to the inductor should be kept equal to ensure proper operation.

Figure 3. Detailed Front Page Application (All 1A Outputs)

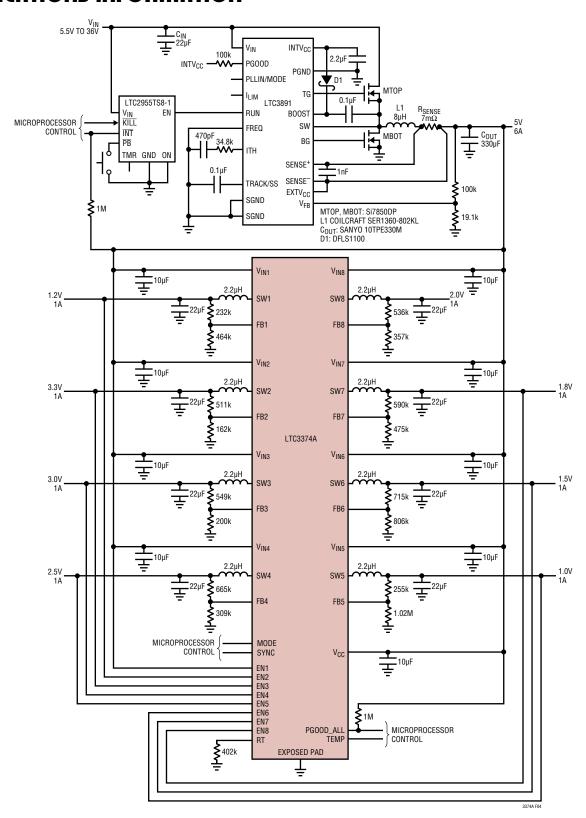

Figure 4. Buck Regulators with Sequenced Start-Up Driven from a High Voltage Upstream Buck Converter (All 1A Outputs)

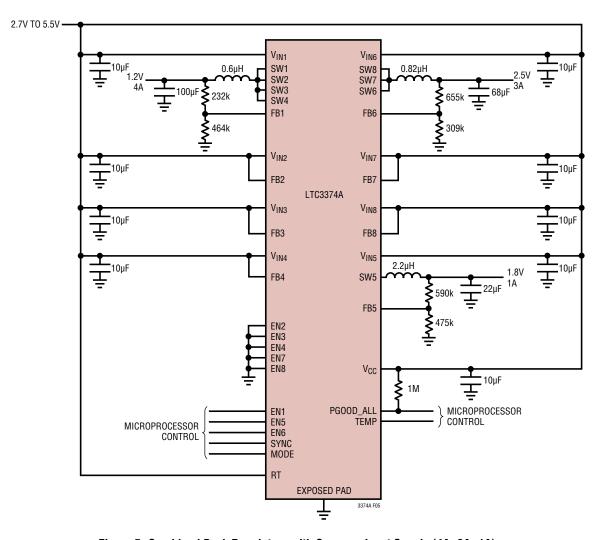

Figure 5. Combined Buck Regulators with Common Input Supply (4A, 3A, 1A)

#### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/products/LTC3374A#packaging for the most recent package drawings.

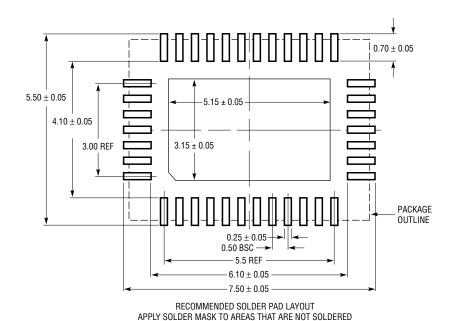

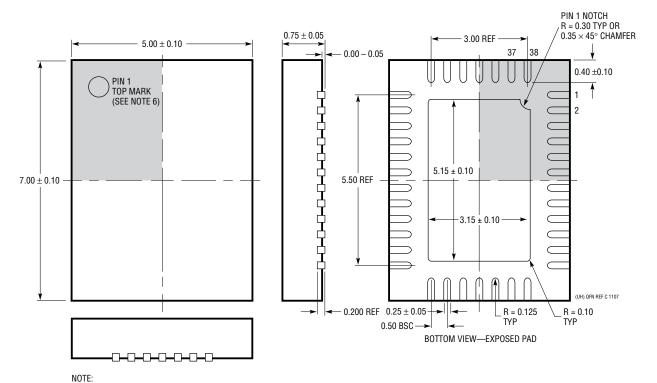

# $\begin{array}{c} \text{UHF Package} \\ \text{38-Lead Plastic QFN (5mm} \times 7\text{mm)} \end{array}$

(Reference LTC DWG # 05-08-1701 Rev C)

- 1. DRAWING CONFORMS TO JEDEC PACKAGE OUTLINE MO-220 VARIATION WHKD

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.20mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

3374af

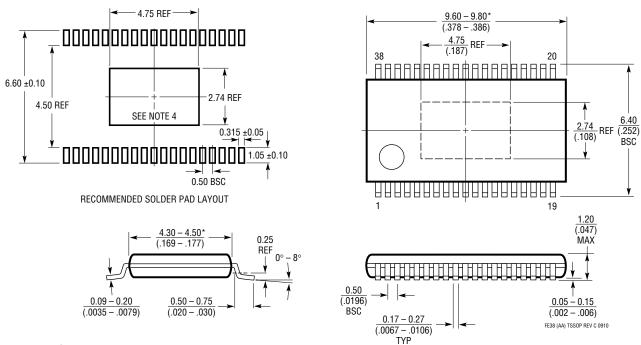

#### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/products/LTC3374A#packaging for the most recent package drawings.

#### FE Package 38-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1772 Rev C)

**Exposed Pad Variation AA**

NOTE:

- 1. CONTROLLING DIMENSION: MILLIMETERS

2. DIMENSIONS ARE IN MILLIMETERS

- (INCHES)

- 3. DRAWING NOT TO SCALE

- 4. RECOMMENDED MINIMUM PCB METAL SIZE FOR EXPOSED PAD ATTACHMENT

- \*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.150mm (.006") PER SIDE

#### TYPICAL APPLICATION

Combined Bucks with 3MHz Switching Frequency and Sequenced Power Up (3A, 1A, 2A, 2A)

## **RELATED PARTS**

| PART NUMBER         | DESCRIPTION                                                | COMMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC3370/<br>LTC3371 | 4-Channel 8A<br>Configurable 1A Buck<br>DC/DCs             | Four Synchronous Buck Regulators with 8 × 1A Power Stages. Can Connect Up to Four Power Stages in Parallel to Make a High Current Output (4A Maximum) with a Single Inductor, 8 Output Configurations Possible, Precision PG00D Indication. LTC3371 has a watchdog timer. LTC3370: 32-Lead 5mm × 5mm QFN. LTC3371: 38-Lead 5mm × 7mm QFN and TSSOP                                                                                                                                |

| LTC3374/<br>LTC3375 | 8-Channel Parallelable<br>1A Buck DC/DCs                   | Eight 1A Synchronous Buck Regulators. Can Connect Up to Four Power Stages in Parallel to Make a High Current Output (4A Maximum) with a Single Inductor, 15 Output Configurations Possible. LTC3375 has I <sup>2</sup> C programming with a watchdog timer and pushbutton. LTC3374: 38-Lead 5mm × 7mm QFN and TSSOP. LTC3375 48-Lead 7mm × 7mm QFN                                                                                                                                |

| LTC3589             | 8-Output Regulator with<br>Sequencing and I <sup>2</sup> C | Triple I <sup>2</sup> C Adjustable High Efficiency Step-Down DC/DC Converters: 1.6A, 1A, 1A. High Efficiency 1.2A Buck-Boost DC/DC Converter, Triple 250mA LDO Regulators. Pushbutton On/Off Control with System Reset, Dynamic Voltage Scaling and Slew Rate Control. Selectable 2.25MHz/1.12MHz Switching Frequency, 8µA Standby Current, 40-Lead 6mm × 6mm QFN.                                                                                                                |

| LTC3675             | 7-Channel Configurable<br>High Power PMIC                  | Four Synchronous Buck DC/DCs (1A/1A/500mA/500mA). Buck DC/DCs Can Be Paralleled to Deliver Up to 2A with a Single Inductor. Independent 1A Boost and 1A Buck-Boost DC/DCs, Always-On 25mA LDO. Dual String I $^2$ C Controlled 40V LED Driver. I $^2$ C Programmable Output Voltage and Read Back of DC/DC, Operating Mode, and Switch Node Slew Rate for All DC/DCs. Fault Status, Pushbutton On/Off/Reset, Low Quiescent Current: 16µA (All DC/DCs Off), 4mm × 7mm 44-Lead QFN. |

LT 0716 • PRINTED IN USA

LINEAR TECHNOLOGY

© LINEAR TECHNOLOGY CORPORATION 2016